PaulStoffregen

Well-known member

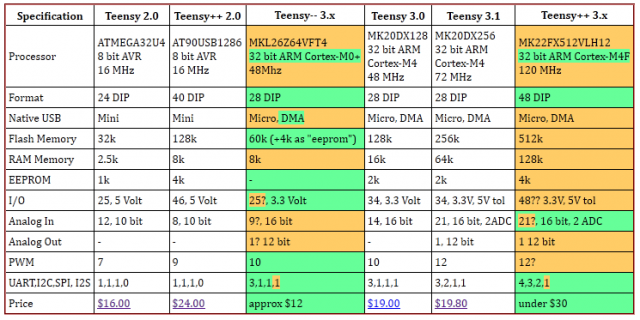

The low cost board will have 60K flash (4K will be reserved for EEPROM emulation). Sorry Steve, but trade-offs had to be made to keep the cost low. We're absolutely locked into 60K at this point in time.

Overall, I think it's going to be a great product. Today there are a lot of low-cost dev boards featuring the ATTINY chips, which are terribly feature poor. The intention of is to offer a LOT more capability "for only a little more $$" than boards like Adafruit Trinket & Gemma and Chinese clones of Arduino Nano & Leonardo. It will have good USB performance (DMA-based) and still a rich peripheral set (3 serial, I2C, SPI, 10 PWM, many ADC pins, etc) and enough memory to allow for excellent compatibility with nearly all Arduino libraries.

You can't have everything on the cheaper low-end product. 5V tolerance, large memory, and CPU speed will be the main differences.

Overall, I think it's going to be a great product. Today there are a lot of low-cost dev boards featuring the ATTINY chips, which are terribly feature poor. The intention of is to offer a LOT more capability "for only a little more $$" than boards like Adafruit Trinket & Gemma and Chinese clones of Arduino Nano & Leonardo. It will have good USB performance (DMA-based) and still a rich peripheral set (3 serial, I2C, SPI, 10 PWM, many ADC pins, etc) and enough memory to allow for excellent compatibility with nearly all Arduino libraries.

You can't have everything on the cheaper low-end product. 5V tolerance, large memory, and CPU speed will be the main differences.