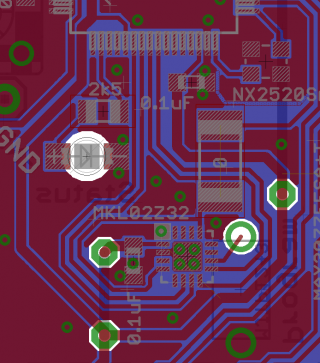

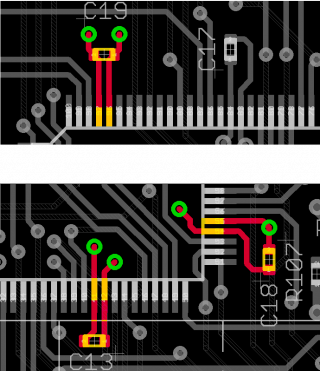

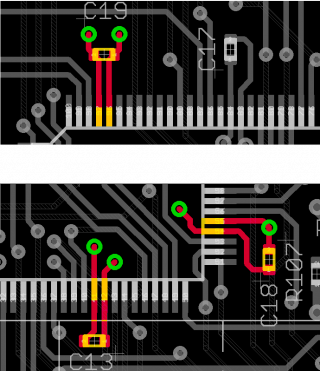

I've been somewhat ignorant when it comes to the finer details of pcb layout. Recently I browse through a couple of books that try their best to make me clear. Here is a couple of examples of a recent board of mine, and I have highlighted three of the decoupling caps. The MCU is a LQFP100 package and the caps are 100nF in 0402 packages. The vias connect to ground and power plane.

The top cap (C19) is placed according to best practices (as I understand them). The other two are not. I haven't noticed any problems. But then again the board has never been outside the lab.

I guess my question is: How big a deal is this? As long as the tracks are short, does it matter?

The Vref pins (reference voltage for the ADC) also have a 100nF cap across them. Vref+ comes from an onboard TL431 shunt regulator. Vref- goes to ground. Do they require special treatment like shielding or local ground?

The top cap (C19) is placed according to best practices (as I understand them). The other two are not. I haven't noticed any problems. But then again the board has never been outside the lab.

I guess my question is: How big a deal is this? As long as the tracks are short, does it matter?

The Vref pins (reference voltage for the ADC) also have a 100nF cap across them. Vref+ comes from an onboard TL431 shunt regulator. Vref- goes to ground. Do they require special treatment like shielding or local ground?