onehorse

Well-known member

Since Frank B made the suggestion for a memory board add-on or some such, I would like to follow up by asking what such an add-on board might look like. For my purposes two I2C 256 kByte EEPROMs have been plenty but I recognize that some would like 1) more memory, 2) faster, and 3) communications via an SPI port.

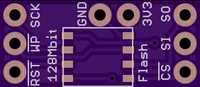

I would like to keep the board small, say 0.3 in x 0.7 in (3-pin positions wide) or possibly 0.4 in x 0.7 in (4-pin positions wide) although the latter might interfere with the I2C port at pins 16/17 on Teensy 3.x (maybe not a problem on Teensy LC).

This means using 5 mm x 6 mm WSON packages, which for flash memory allows up to 128 Mbit of 16 Mb of fast (~100 MHz) memory. I have ordered some of these flash chips from Digikey (Spansion and Winbond) and will design a simple add-on for testing purposes and for me to get familiar writing sketches using SPI.

One attractive possibility is to use digitalWrite (HIGH/LOW) to power the add-on board as I have done in other instances where the power draw is much less that 10 mA. This would make it easier to design if I don't have to take power from the end 3V3/GND pins.

But I would appreciate some input: what would the "optimum" memory add-on board for Teensy 3.x/LC look like given the 1) small size and 2) SPI constraints?

If we can reach some kind of consensus I would be happy to design, assemble, and offer for sale such a board.

I would like to keep the board small, say 0.3 in x 0.7 in (3-pin positions wide) or possibly 0.4 in x 0.7 in (4-pin positions wide) although the latter might interfere with the I2C port at pins 16/17 on Teensy 3.x (maybe not a problem on Teensy LC).

This means using 5 mm x 6 mm WSON packages, which for flash memory allows up to 128 Mbit of 16 Mb of fast (~100 MHz) memory. I have ordered some of these flash chips from Digikey (Spansion and Winbond) and will design a simple add-on for testing purposes and for me to get familiar writing sketches using SPI.

One attractive possibility is to use digitalWrite (HIGH/LOW) to power the add-on board as I have done in other instances where the power draw is much less that 10 mA. This would make it easier to design if I don't have to take power from the end 3V3/GND pins.

But I would appreciate some input: what would the "optimum" memory add-on board for Teensy 3.x/LC look like given the 1) small size and 2) SPI constraints?

If we can reach some kind of consensus I would be happy to design, assemble, and offer for sale such a board.