Custom Teensy 4.1 Bootloader issues

Hi All,

Thank-you in advance for any help / guidance you can provide. I'm having trouble with a custom T4.1.

The issue is that pressing the program button on the device, rarely (about 5% of the time) causes the device to program. The other 95% of the time when I press the program button on the device, the bootloader LED flashes 3 times, and then the device reboots without loading HalfKay. Instead it just runs the code that's already on the device and the bootloader flash sequence never repeats.

I'm not sure where to start looking. I'm think it's probably a signal integrity issue, but I don't know where to start.

Board Specs

4-layer 1.6mm, signal, GND, VCC, signal

Suspect 1: Flash Layout

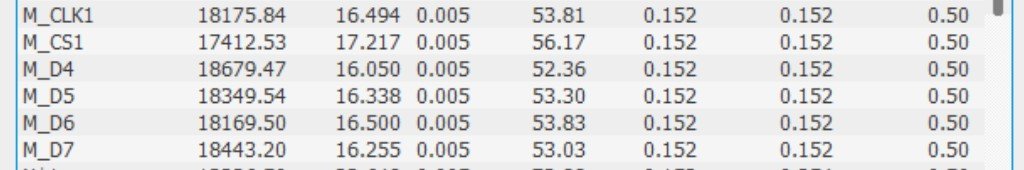

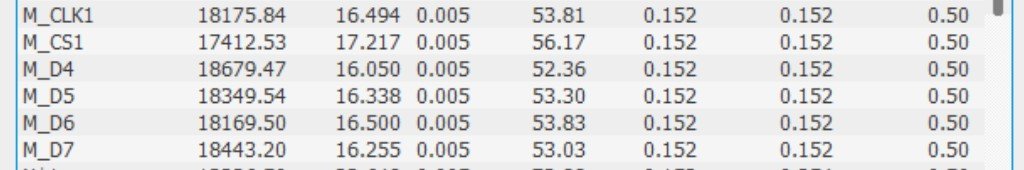

Here's a the measurements of my data and clock lines for the SPI Flash.

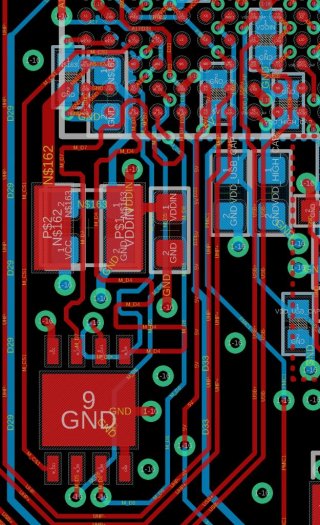

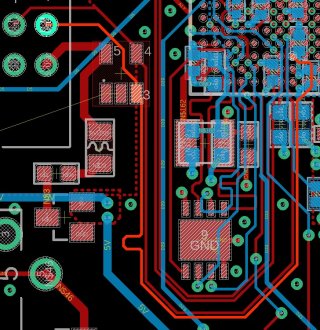

And here's the Flash Memory layout. I tried to mimic the T4.1 design as much as possible.

Suspect 2: Bootloader Layout:

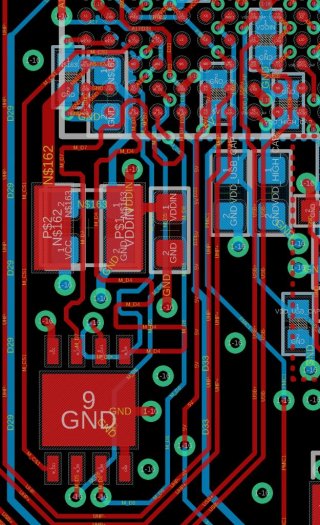

I'm showing this one from layer 4 because most of the signals to the bootloader are routed there.

Suspect 3: USB D+/D- lines

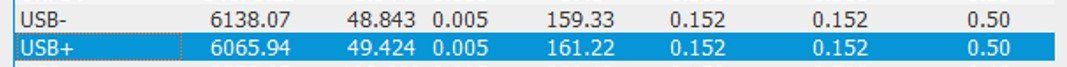

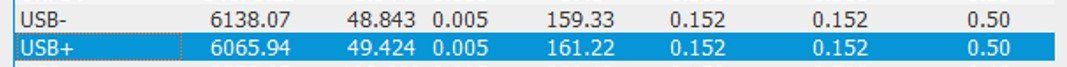

Here are the trace specs. I wonder if the thin trace width is part of the problem. They are spaced 5mils apart.

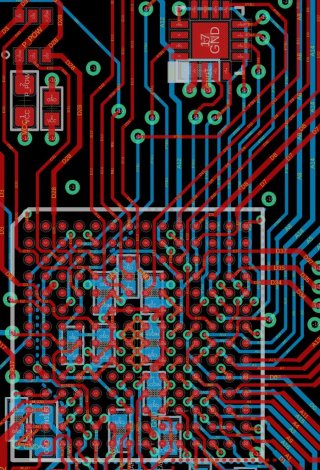

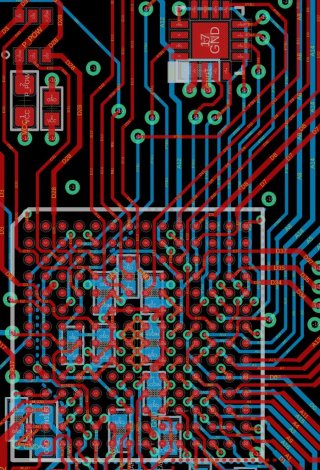

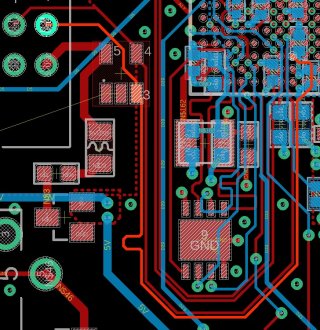

And here is the USB data lines layout.

I'm really at a loss as to how to solve my problem. I would greatly appreciate any help.

Hi All,

Thank-you in advance for any help / guidance you can provide. I'm having trouble with a custom T4.1.

The issue is that pressing the program button on the device, rarely (about 5% of the time) causes the device to program. The other 95% of the time when I press the program button on the device, the bootloader LED flashes 3 times, and then the device reboots without loading HalfKay. Instead it just runs the code that's already on the device and the bootloader flash sequence never repeats.

I'm not sure where to start looking. I'm think it's probably a signal integrity issue, but I don't know where to start.

Board Specs

4-layer 1.6mm, signal, GND, VCC, signal

Suspect 1: Flash Layout

Here's a the measurements of my data and clock lines for the SPI Flash.

And here's the Flash Memory layout. I tried to mimic the T4.1 design as much as possible.

Suspect 2: Bootloader Layout:

I'm showing this one from layer 4 because most of the signals to the bootloader are routed there.

Suspect 3: USB D+/D- lines

Here are the trace specs. I wonder if the thin trace width is part of the problem. They are spaced 5mils apart.

And here is the USB data lines layout.

I'm really at a loss as to how to solve my problem. I would greatly appreciate any help.

Last edited: