jbliesener

Well-known member

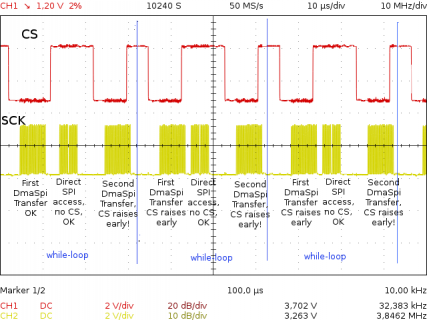

I already tried lots of things:

Nothing really helped... Maybe it's a matter of sequencing those blocks correctly, but I admit that I'm lost...

Code:

while (SPI0_TCR!=tcrEnd); // wait for last increment of TCR

SPI0_SR = SPI_SR_TCF; // reset TCF

// clear DMA int

DMA_CINT = DMA_CINT_CINT(DMASPI0_RXCHAN);

DMA_CERQ = DMA_CERQ_CERQ(DMASPI0_TXCHAN);

// reset SPI

SPI0_SR = 0xFF0F0000;

SPI0_MCR |= SPI_MCR_CLR_RXF | SPI_MCR_CLR_TXF;

SPI0_TCR = 0;Nothing really helped... Maybe it's a matter of sequencing those blocks correctly, but I admit that I'm lost...