The I²C specifications (NXP, I²C-bus.org) allow the slave to set the SCL clock line low to make the master wait. This is called clock streching.

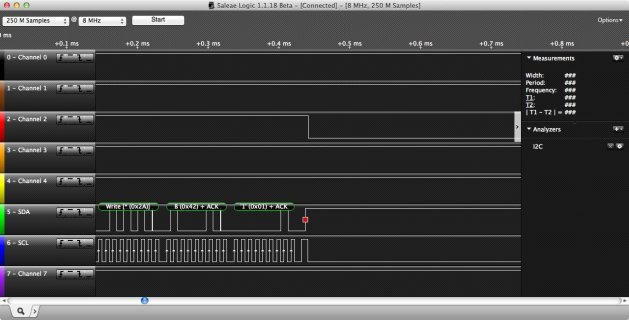

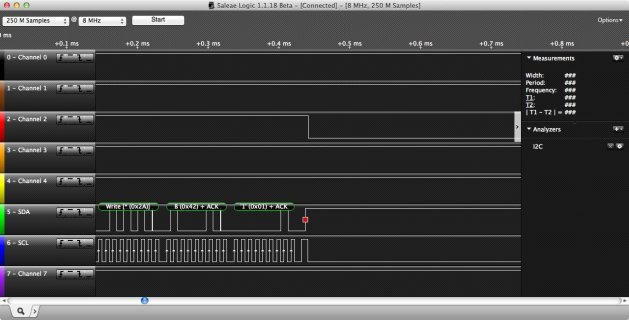

I tested this implementation on a Teensy 3.0 with my Saleae logic analyser:

I haven't found the Wire library at the Teensy Core Libraries for Arduino PaulStoffregen/cores repository on GitHub.

Please feel free to test the code and add it to the library.

An I2C slave is allowed to hold down the clock if it needs to reduce the bus speed. The master on the other hand is required to read back the clock signal after releasing it to high state and wait until the line has actually gone high.

I tested this implementation on a Teensy 3.0 with my Saleae logic analyser:

- Add to Wire.h

Code:

void pause();

void resume();- Add to Wire.cpp

Code:

void TwoWire::pause()

{

volatile uint32_t *config;

config = portConfigRegister(SCL);

*portModeRegister(SCL) = 1;

*config = PORT_PCR_SRE | PORT_PCR_DSE | PORT_PCR_MUX(1);

*portClearRegister(SCL) = 1;

}

void TwoWire::resume()

{

CORE_PIN19_CONFIG = PORT_PCR_MUX(2)|PORT_PCR_ODE|PORT_PCR_SRE|PORT_PCR_DSE;

*portSetRegister(SCL) = 1;

}I haven't found the Wire library at the Teensy Core Libraries for Arduino PaulStoffregen/cores repository on GitHub.

Please feel free to test the code and add it to the library.