OK,

I have the following issue

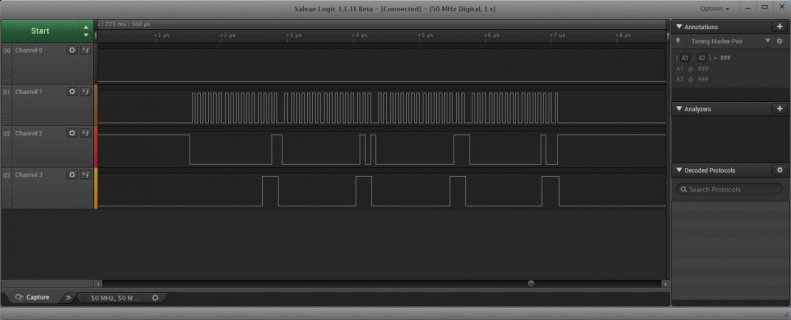

A Teensy3.1 T1 is SPI-master and transfer data to Teensy3.1 T2, configured as slave and receive simultaneously data from T2.

As the process has to run in parallel to the CPU, I use DMA.

Observation:

T1 receives correctly data from T2 (slave sends different data than master) and DMA completion ISR (RX) is called. So T2 sends data also in slave mode.

T2, however, never calls DMA completion ISR (RX).

As my SW is completely in C, code here does not help and may not be necessary.

So I have two questions:

1st: Did someone had similar issues and found a solution?

2nd: Is there a stable 'official' teensy SPI-DMA (master/slave) library I could use to provide code that could be read/tested by others?

Gazie,

Walter

I have the following issue

A Teensy3.1 T1 is SPI-master and transfer data to Teensy3.1 T2, configured as slave and receive simultaneously data from T2.

As the process has to run in parallel to the CPU, I use DMA.

Observation:

T1 receives correctly data from T2 (slave sends different data than master) and DMA completion ISR (RX) is called. So T2 sends data also in slave mode.

T2, however, never calls DMA completion ISR (RX).

As my SW is completely in C, code here does not help and may not be necessary.

So I have two questions:

1st: Did someone had similar issues and found a solution?

2nd: Is there a stable 'official' teensy SPI-DMA (master/slave) library I could use to provide code that could be read/tested by others?

Gazie,

Walter