PaulStoffregen

Well-known member

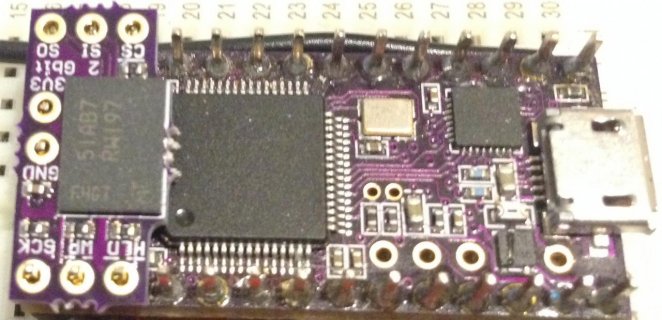

Oh, yeah, for other chips with the QSPI ports, you'd want access to those 2 pins.

Today relatively few microcontrollers have QSPI, but it's probably going to become more common over the next few years.

Today relatively few microcontrollers have QSPI, but it's probably going to become more common over the next few years.