have you played with any of the FRAM chips?

When I get back from travel there are two FRAMs waiting for me (one small and fast SPI, one large and slow I2C)

have you played with any of the FRAM chips?

Be sure to program the serial flash chips in block mode of course. the single byte/word program (which assumes it's writing to an erased byte/word), is much slower due to overhead.

Probably not enough I/O bits, but I'm using the industry standard FSMC parallel interface for NAND flash. Some ARMs have an FSMC controller chip on the ARM. It takes 8 fdata bits (or 16) to do FSMC, but it is very fast. FMSC also has a mode in the ARMs and the flash to fetch instructions from FSMC flash. I think it's used to run boot mode code.

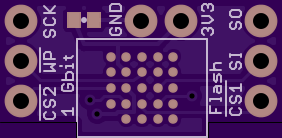

Question for those of you in the know, would it be effective to leverage the extra SPI channels on the Teensy 3.1 to read or write to 1 chip while the other erases?

not that i'm in the know, but sure, i guess, depending on what's the application, you could come up with a scheduling scheme where you have two or more of those w25 chips going on, using different CSs (there's only one SPI, effectively (?)); you just couldn't move from A to B to A very fast; we're talking about 5-10 seconds for the complete erase; i haven't tried any of the block/sector erase modes.

Reason I said that was I was under the impression you had to leave CS pulled low while the chips erase, after reading the Microchip datasheet that does not seem to be the case(and winbonds). After you clock in the command and address for the erase you pull CS high and it executes the erase. Meaning you can set it to erase a page/sector/block/whatever and then go do other things, then just poll it every once in a while and it will let you know when its ready to do more work.

void flash_chip_erase(boolean wait)

{

write_pause();

// Send Write Enable command

digitalWrite(f_cs, LOW);

SPI.transfer(CMD_WRITE_ENABLE);

digitalWrite(f_cs, HIGH);

digitalWrite(f_cs, LOW);

SPI.transfer(CMD_CHIP_ERASE);

digitalWrite(f_cs, HIGH);

flash_wait_for_write = 1;

if(wait)write_pause();

}yeah, that was my understanding too. here's the erase from el supremo's 'flash_spi' code:

Code:void flash_chip_erase(boolean wait) { write_pause(); // Send Write Enable command digitalWrite(f_cs, LOW); SPI.transfer(CMD_WRITE_ENABLE); digitalWrite(f_cs, HIGH); digitalWrite(f_cs, LOW); SPI.transfer(CMD_CHIP_ERASE); digitalWrite(f_cs, HIGH); flash_wait_for_write = 1; if(wait)write_pause(); }

Can you drop a link to the full code, I cant seem to find it :/

good question. i think it came with one of the earlier versions of the audio library but seems to be gone now.

my copy is here:

https://github.com/mxmxmx/eurotrash/blob/master/soft/libraries/Audio/flash_spi.cpp

Just a quick observation. He used alot of digitalWrite High/Low transitions for CS pin, a normal digitalWrite High then Low takes about 750nS or 1.5uS full cycle if you where bit banging it on and off constantly. A digitalWriteFast High to Low takes about 10nS and if you need more time you add extra digitalWriteFast's to it. Since even the Teensy 3.0 can handle 25Mhz SPI its a waste to kill so much time just to transition a CS pin.

Yes, some years ago. I could'nt get a serial RAM, for my stm32-webradio. But i needed a large buffer. Maybe a bit unconventional to use FRAM as RAM only, but it was okAnd Frank B have you played with any of the FRAM chips?

Just a quick observation. He used alot of digitalWrite High/Low transitions for CS pin, a normal digitalWrite High then Low takes about 750nS or 1.5uS full cycle if you where bit banging it on and off constantly. A digitalWriteFast High to Low takes about 10nS and if you need more time you add extra digitalWriteFast's to it. Since even the Teensy 3.0 can handle 25Mhz SPI its a waste to kill so much time just to transition a CS pin.

Should we consider a separate thread so we aren't derailing onehorse's hardware discussion with software chat?

Some of the larger Spansions call for up to 100mA of current.

Are you writing ontop of existing data(which requires it to erase then write)?

Or are you writing to already erased pages/sectors?

One major drawback to the larger storage chips is that you end up having to erase larger and larger minimums of storage.

Sorry missed this question: Easily answered.

In my case, at the moment, I'm using 4.5Mbytes for one set of samples for 16 pads. But I need an additional set for another 16 for a standard drumset at least, plus a collection of loops/samples for beatmashing.

So basically I'm already full, having reduced my samples to mono and shortened some of them against my wishes.

So yes, to apply a new patch with different samples for another track, would require a wipe & flash new data from the SDCard, largely to the whole chip.

My reasoning behind the 128Mbyte chip is that I could conceivably provide 15 sound patches for finger drumming, 10 drumkits, and a large collection of loops, and have this all flashed to the one chip, allowing any track to use any sample, at any given time, as much as they like.

One could then allow soundpacks which flash the entire chip with all new sounds, but it would not be considered as a live event. you would build your set on the contents of a single soundpack.

This is my dream, and whether it will ever be realised (i think it will) is not sure, but it would definitely be a shame to have 250Mhz or more on the Teensy 3++/4 or what have you, chewing through bits like lightning, only to end up running out of bits to chew.

Not sure what you mean with "audioexpander", but if you're talking about the SGTL500: It uses I2S for Audiodata. I2S != I2C !!! I2C is for control only.From what I understand the Audio expander uses I2C, which is much slower then the up to 25Mhz you can get out of the SPI.

Not sure what you mean with "audioexpander", but if you're talking about the SGTL500: It uses I2S for Audiodata. I2S != I2C !!! I2C is for control only.

FRAM is a great solution, no erase-time, fast access-time. but very expensive.

Edit: and small.

http://www.digikey.com/product-highlights/us/en/ramtron-fm25v20-f-ram-memory/2675

I can see occasions where the extra ram space and speed of the FRAM would be more useful then massive amounts of space with slow periodic erases.

that's why the 23LC1024 cropped up further up-thread. it's more or less pin compatible with the W25Q128FV. either can/could be used with the audio board; the latter for storage, the former for longer delay lines etc; at least that was the idea, i guess.