You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Memory board add-on requirements

- Thread starter onehorse

- Start date

- Status

- Not open for further replies.

PaulStoffregen

Well-known member

onehorse - Do you have any of the larger chips handy? Could you run a test program for me, to read their ID bytes?

edit: here's the test:

edit: here's the test:

Code:

#include <SPI.h>

#define CSPIN 6

void setup() {

// comment these out if using the normal SPI pins

SPI.setSCK(14); // Audio shield has SCK on pin 14

SPI.setMOSI(7); // Audio shield has MOSI on pin 7

SPI.begin();

pinMode(CSPIN, OUTPUT);

digitalWrite(CSPIN, HIGH);

while (!Serial) ;

delay(100);

Serial.print("ID bytes: ");

uint8_t id[3];

SPI.beginTransaction(SPISettings(50000000, MSBFIRST, SPI_MODE0));

digitalWrite(CSPIN, LOW);

SPI.transfer(0x9F);

id[0] = SPI.transfer(0);

id[1] = SPI.transfer(0);

id[2] = SPI.transfer(0);

digitalWrite(CSPIN, HIGH);

SPI.endTransaction();

Serial.printf("%02X %02X %02X\n", id[0], id[1], id[2]);

}

void loop() {

}

Last edited:

onehorse

Well-known member

I am in Oregon right now and don't have any with me. I can tell you that the Audio SPI test code modified for me by Frank B returns the first four bytes of the ID correctly for the 128 Mbit flash chip. Presumably also the 1 Gbit Spansion (I got four bytes, the first two look right for the device ID but I haven't verified all four are correct) flash chip. I'll be able to do more extensive testing on Saturday.

PaulStoffregen

Well-known member

I need to figure out how to identify the total capacity, and the block erase size supported by the D8h or DCh commands.

This is the info in Micron 2gb datasheet for capacity from the 3rd ID byte:

22h = 2Gb

21h = 1Gb

20h = 512Mb

19h = 256Mb

18h = 128Mb

17h = 64Mb

Looks like the formula for total bytes capacity was 2 raised to the power of the the ID byte, until someone decided to skip 0x1A through 0x1F.

So far, except for Spansion, every chip seems to support 64K blocks. Some of the very old chips don't, but they're long obsolete now. Many of them also still support 4K sectors, but erasing large amount of memory in 4K sectors is extremely slow on modern parts, so I'm probably not going to bother with 4K sectors.

Looks like Spansion decided to go to 256K blocks at some capacity, maybe 512gb. Some of their smaller chips can apparently be ordered with slightly different part numbers, for either 64k or 256k block erase. I'm not sure if I'll go to the trouble to detect these. Guess we'll just have to see if anyone actually gets one of them....

This is the info in Micron 2gb datasheet for capacity from the 3rd ID byte:

22h = 2Gb

21h = 1Gb

20h = 512Mb

19h = 256Mb

18h = 128Mb

17h = 64Mb

Looks like the formula for total bytes capacity was 2 raised to the power of the the ID byte, until someone decided to skip 0x1A through 0x1F.

So far, except for Spansion, every chip seems to support 64K blocks. Some of the very old chips don't, but they're long obsolete now. Many of them also still support 4K sectors, but erasing large amount of memory in 4K sectors is extremely slow on modern parts, so I'm probably not going to bother with 4K sectors.

Looks like Spansion decided to go to 256K blocks at some capacity, maybe 512gb. Some of their smaller chips can apparently be ordered with slightly different part numbers, for either 64k or 256k block erase. I'm not sure if I'll go to the trouble to detect these. Guess we'll just have to see if anyone actually gets one of them....

These SPI flash chips all have discoverable via JEDEC standard commands, to find the chip sizing, sector size list, etc. Some chips have one time programmable bits to change the lower or upper sector(s) from many small sectors to uniform size for all sectors. The rationale for the small sectors is for things like metadata (file system directories), instead of or addition to linked lists that grow into erased but as yet unwritten bytes.

Some have two dies in one package, with two SS pins - but to software they look like independent "chips", where chip does not mean integrated circuit package.

It's a bit of code to write, to read the JEDEC parameters. Just reading the manufacturer ID 3 byte code won't tell you how the uniform-size vs. small-size regions have been setup in the OTP.

Some have two dies in one package, with two SS pins - but to software they look like independent "chips", where chip does not mean integrated circuit package.

It's a bit of code to write, to read the JEDEC parameters. Just reading the manufacturer ID 3 byte code won't tell you how the uniform-size vs. small-size regions have been setup in the OTP.

PaulStoffregen

Well-known member

These SPI flash chips all have discoverable via JEDEC standard commands, to find the chip sizing, sector size list, etc.

The very newest ones certainly do. But many older-but-still-selling chips provide only a few bytes of identification.

For example, it was added after W25Q128 was already made:

8.2.30 Read SFDP Register (5Ah)

The W25Q128BV features a 256-Byte Serial Flash Discoverable Parameter (SFDP) register that contains information about device configurations, available instructions and other features. The SFDP parameters are stored in one or more Parameter Identification (PID) tables. Currently only one PID table is specified, but more may be added in the future. The Read SFDP Register instruction is compatible with the SFDP standard initially established in 2010 for PC and other applications, as well as the JEDEC standard JESD216 that is published in 2011. Most Winbond SpiFlash Memories shipped after June 2011 (date code 1124 and beyond) support the SFDP feature as specified in the applicable datasheet.

None of the smaller chips seem to have ID beyond the 3 bytes from the 9Fh command.

onehorse

Well-known member

I just redesigned the 1 Gbit SPI flash board to use the N25Q00AA Micron chip with one CS. This new board will be made available for sale at Tindie in a few weeks.

The same design can accomodate the 2 Gbit Micron chip also, but I am not sure whether the demand for the extra 1 Gbit justifies the doubling in cost for this new chip. We'll see...

The same design can accomodate the 2 Gbit Micron chip also, but I am not sure whether the demand for the extra 1 Gbit justifies the doubling in cost for this new chip. We'll see...

mixania

Member

I just redesigned the 1 Gbit SPI flash board to use the N25Q00AA Micron chip with one CS. This new board will be made available for sale at Tindie in a few weeks.

Great job, am looking forward to it.

The same design can accomodate the 2 Gbit Micron chip also, but I am not sure whether the demand for the extra 1 Gbit justifies the doubling in cost for this new chip. We'll see..

1Gbit sounds more than necessary I would say

PaulStoffregen

Well-known member

I just redesigned the 1 Gbit SPI flash board to use the N25Q00AA Micron chip

Most excellent. The Micron chip looks really, really nice.

I'm guessing you're not adding a 9V boost converter to the board? It only reduces the write & erase time about about 20%, according to the specs.

perhaps replace the N25Q00AA with the Macronix MX66L1G45G

http://www.macronix.com/Lists/Appli... Micron N25Q00AA with Macronix MX66L1G45G.pdf

http://www.macronix.com/Lists/Appli... Micron N25Q00AA with Macronix MX66L1G45G.pdf

Looks like writing software is easier...4-5. Chip Read and Erase Differences

The Micron N25Q00A only supports the Die Erase func

tion, which means users have to execute four Die

Erase Commands (once in each die) to finish a chip

erase operation. In the meantime, The Macronix

MX66L1G45G device looks and works like a monolithic

1Gb die and only needs one CE command with

no address required.

Similarly, because Micron treats its four die solut

ion as four independently addressable arrays, extra

steps may be required when using the Micron flash d

uring Reads which are not required for the Macronix

flash. For example, per the Micron datasheet "After

any READ command is executed, the device will

output data from the selected address in the die. A

fter a die boundary is reached, the device will sta

rt

reading again from the beginning of the same 256Mb

die. A complete device reading is completed by

executing READ four times.." Macronix has no such

requirement: “the whole memory can be read out

with a single READ instruction. The address counter

rolls over to 0 when the highest address has been reached"

onehorse

Well-known member

not adding a 9V boost converter to the board?

No, not added. I want to keep it simple, but if there is a compelling reason to do so I can.

replace the N25Q00AA with the Macronix MX66L1G45G

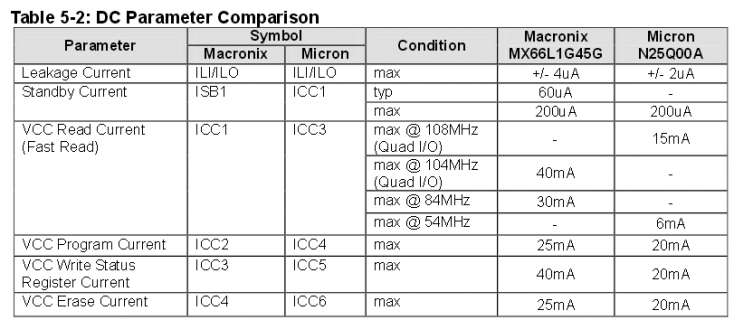

I considered it, but the current usage for the Macronix chip is significantly (20 - 100% in some cases) higher, so I decided against. Not sure the software advantage is really compelling...

Last edited:

It means that it's a bit complicated to use SPI with FIFO when crossing the die-boundaries.

@Paul, what do you think ?

Edit:Current: I don't know.. leakage is only 2ua more,standby the same, and the teensy can use only 1/3 of the speed, so the max-read/write current should be less

Edit: Idea: Can you use "jumpers" for HOLD and WP ? That would make it possible to free the pins for other purposes.

@Paul, what do you think ?

Edit:Current: I don't know.. leakage is only 2ua more,standby the same, and the teensy can use only 1/3 of the speed, so the max-read/write current should be less

Edit: Idea: Can you use "jumpers" for HOLD and WP ? That would make it possible to free the pins for other purposes.

Last edited:

PaulStoffregen

Well-known member

It means that it's a bit complicated to use SPI with FIFO when crossing the die-boundaries.

@Paul, what do you think ?

The erase command should be fairly easy to accommodate. I had actually ordered this chip recently and it arrived today, so I'll begin testing it soon.

I'm not aware of any other die boundary issues for reading. Did I miss something?

PaulStoffregen

Well-known member

Oh, I see that now. Yes, that is an unpleasant detail. I'm seeing it on page 43 of the datasheet now too. Unfortunately, I think this isn't something which can be easily ignored.

The code is already bringing a byte in for the 24 vs 32 bit mode flag. It'll make the source messy, but I think this same byte could be used for more info. There's also a problem where Spansion chips use different commands for suspend. All this stuff needs to get supported, but my hope is to do so without hurting the read latency of all the other chips.

It's really unfortunate all these semiconductor manufacturers couldn't standardize better, especially Spansion. It is going to make for more complex code, but I think with a little trickery it can be done with little or no significant impact on performance. It is going to code a bit more in code size though.

The code is already bringing a byte in for the 24 vs 32 bit mode flag. It'll make the source messy, but I think this same byte could be used for more info. There's also a problem where Spansion chips use different commands for suspend. All this stuff needs to get supported, but my hope is to do so without hurting the read latency of all the other chips.

It's really unfortunate all these semiconductor manufacturers couldn't standardize better, especially Spansion. It is going to make for more complex code, but I think with a little trickery it can be done with little or no significant impact on performance. It is going to code a bit more in code size though.

PaulStoffregen

Well-known member

Does anyone know where to buy qty 1 or 2 of the Macronix MX66L1G45G chip? I see Future has them in stock, but a 44 piece minimum for the 3.3V version.

BriComp

Well-known member

Does anyone know where to buy qty 1 or 2 of the Macronix MX66L1G45G chip? I see Future has them in stock, but a 44 piece minimum for the 3.3V version.

Try this web page, still Future Electronics http://www.futureelectronics.com/en/Technologies/Product.aspx?ProductID=MX66U51235FZ4I10GMACRONIX8053792&IM=0

PaulStoffregen

Well-known member

Try this web page

They have "MX66L1G45G" in the description, but that seems to be a copy-n-paste error.

The description also says "512 Mb (64 M x 8) 1.65 - 2 V". The part number is "MX66U51235FZ4I-10G", and the datasheet link goes to the datasheet for MX66U51235, not MX66L1G45. The "product highlight" section has 512 Mb, 1.8V specs. The price is also well under the $10-12 point for a 1 Gb chip.

onehorse

Well-known member

Do you have any of the larger chips handy? Could you run a test program for me, to read their ID bytes?

edit: here's the test:

Here is the results:

Spansion S25FL127 128 Mbit 01 20 18

Spansion S70FL01G 1 Gbit 01 02 20 these are both with Chip Select on pin 10; the other 512Mbit is accessible on the S70FL01G by using the Chip Select on pin 15.

Does the complication above mean that Micron's 1 Gbit SPI flash is not as useful as some thought? Should I plan to make this chip available?

And if the Macronix is a winner, I would be willing to buy a significant share of the 44 minimum required for purchase for subsequent sale in an add-on board on Tindie. Thoughts here?

Last edited:

Is it possible to share your library with other on this forum?

I've asked... it was originally written by me as an avocation. Then I expanded what it can do to four different SPI flash chip types.

Then I made the code support an array of SPI flash chips - where the API is not chip select based but rather an address from 0 to size of arrary in bytes. The tricky part is making it seamless, across sector and chip/die boundaries.

It was based on CMSIS/HAL with DMA (not Freescale) and I recently replaced those I/O calls with Arduino's SPI calls. It's very much a step down doing so.

I doubt many forum users need an array of SPI Flash chips (say, 2 or 3 or 4 or more) as I did in this professional work - to store large data items for consumers.

I'll check next week again on the intellectual properties issue.

- Status

- Not open for further replies.