The beaviour of the setup at the moment is as follows:

When I unplug the SD card I can use all seven displays without problems.

When I unplug the displays from the wirenet, I can access the connected SD using SDFAT library without problems.

Connecing two or three displays and the SD card, I can access the SD card and talk to the displays.

Once I connect the SD card and more than two or three displays, I cannot talk to the SD card anymore (but to the displays).

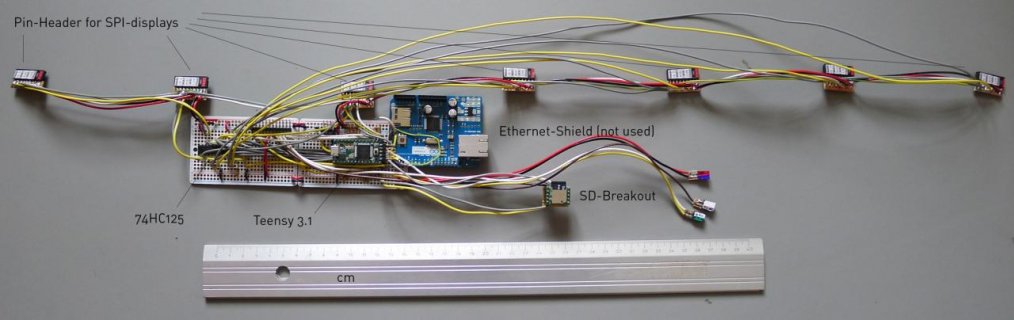

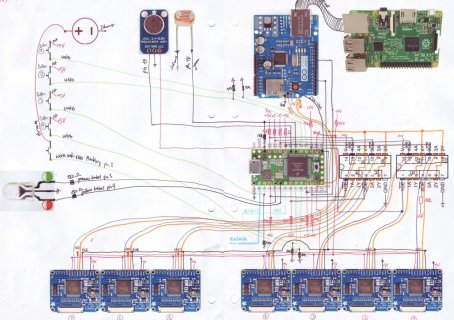

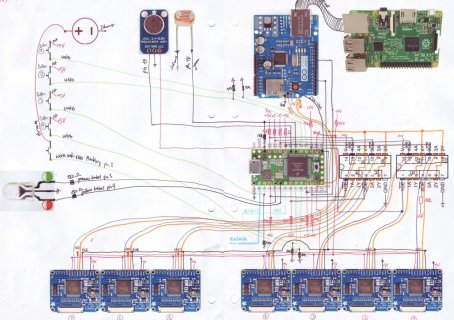

I realize that I'll probably have to rebuild my wirenet ... At the moment, it's a daisy-chain where the connection to the master goes off in the middle of the daisy-chain (see picture below). Is it correct that you suggest a clean daisy-chain that is connected to the master at one end?

BTW: At the moment, I replaced the ethernet shield by a solo SD card breakout board (the one by Paul).

And yes, the slaves do draw a lot of current (250mA per device), so I'll add the capacitors (where would I have to look on how to calculate the ideal capacity?).

At least, both the displays and the SD card run at MODE0 (and it is set accordingly).

I'll use 180 ohm resistors (which I have at home).

A lot of work, thanks for all your suggestions, I'll post more as soon as I'm done trying.

Dani