I am using T3.1 to generate a 500 Hz square wave output with PWM, using the code below. That much works nicely.

The signal is driving my experiment which gives me an analog output. Now I want to use the ADC to sample that voltage at a time which is phase-locked to the PWM signal, with no jitter due to variable interrupt latency. I assume that means using some DMA process that is clocked by the same source as the PWM, or triggering the ADC start time directly from the PWM output. Is this possible? has anyone done anything like this (and published code that I can see?

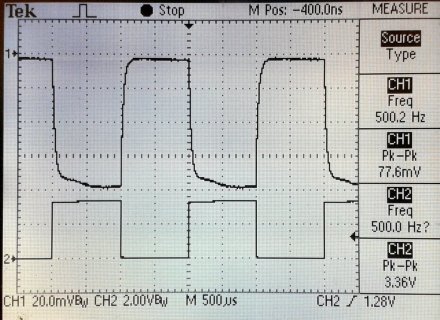

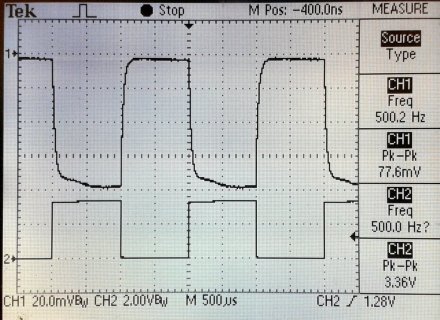

In case of interest, in scope photo below ch.1 is the analog signal (right now it goes negative, but I can fix that) and ch.2 is the 500 Hz PWM out of the Teensy. I want to sample during the last 300 microseconds before each positive and negative edge, but for best stability I want no phase jitter.

...or would it be possible to just schedule the ADC to sample at a steady rate, and then somehow toggle the output based on the ADC sampling? But I think it has to be hardware-triggered to be precisely uniform; eg. same number of clock cycles every time, and a fixed number of cycles between the signal out and the sample points.

Code:

#define FREQ 500 // PWM frequency in Hz

const int OUT1 = 4; // output pin for PWM signal

void setup() {

pinMode(OUT1, OUTPUT);

analogWriteFrequency(OUT1, FREQ); // set PWM frequency in Hz

analogWrite(OUT1, 127); // 50% duty cycle

}

void loop() {}The signal is driving my experiment which gives me an analog output. Now I want to use the ADC to sample that voltage at a time which is phase-locked to the PWM signal, with no jitter due to variable interrupt latency. I assume that means using some DMA process that is clocked by the same source as the PWM, or triggering the ADC start time directly from the PWM output. Is this possible? has anyone done anything like this (and published code that I can see?

In case of interest, in scope photo below ch.1 is the analog signal (right now it goes negative, but I can fix that) and ch.2 is the 500 Hz PWM out of the Teensy. I want to sample during the last 300 microseconds before each positive and negative edge, but for best stability I want no phase jitter.

...or would it be possible to just schedule the ADC to sample at a steady rate, and then somehow toggle the output based on the ADC sampling? But I think it has to be hardware-triggered to be precisely uniform; eg. same number of clock cycles every time, and a fixed number of cycles between the signal out and the sample points.

Last edited: