I'm planning to make Teensy SD adapter with two SRAM chips that can function as temporary buffer to cover the case SD card when is busy with internal activities.

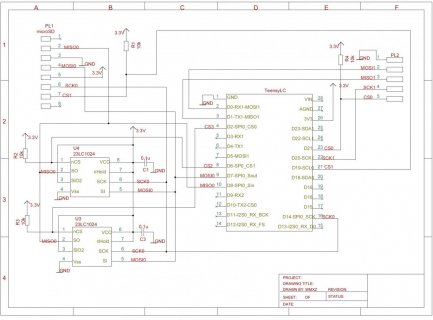

The initial schematic is

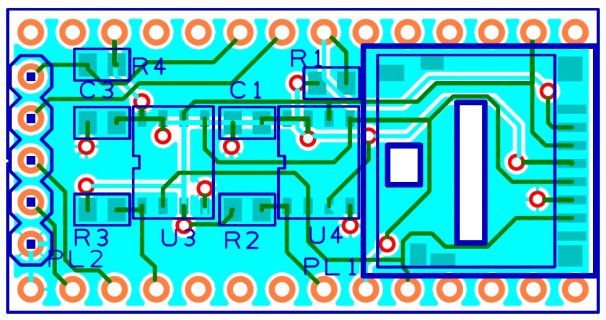

and the dual layer board layout is

In order to be useful for stand alone Teensy, I use spi0 for access to SD-card and SRAM.

In case it is used with TLC external data may be transferred using spi1.

I'm open to comments and suggestions.

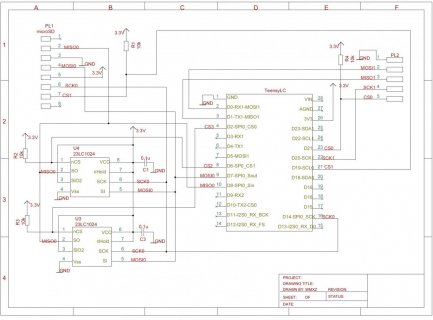

The initial schematic is

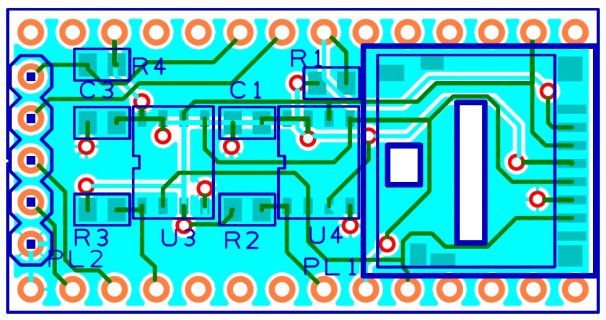

and the dual layer board layout is

In order to be useful for stand alone Teensy, I use spi0 for access to SD-card and SRAM.

In case it is used with TLC external data may be transferred using spi1.

I'm open to comments and suggestions.