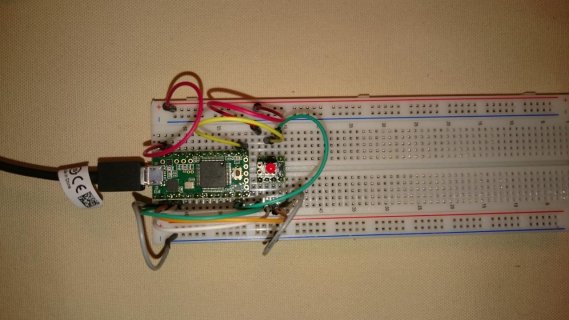

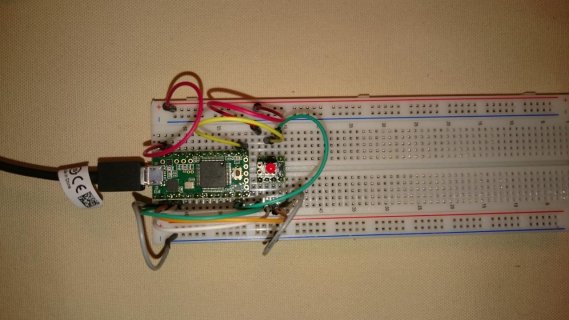

I joined antti at hackaday.io who was developing a tiny breadboard-friendly FPGA board: DIPSY. It has a DIP-8 pinout, plus 6 extra pins which can be accessed from above. See it here together with a Teensy 3.1:

The FPGA has 1284 logic cells and 7 KB RAM, which is enough to create some great peripherals. A simple AVR-ish core eats up about 30 % of the resouces. Also included:

I didn't have any prior FPGA experience but this thing lowered the entry barrier enough for me to give it try. I managed to implement various blinkys, an SPI slave and a WS2812B driver:

There's an arduino library that configures dipsy over SPI, with a configuration stored in a plain C array. No further programming hardware required. The final design is planned to include a configuration flash chip as well.

Regards

Christoph

The FPGA has 1284 logic cells and 7 KB RAM, which is enough to create some great peripherals. A simple AVR-ish core eats up about 30 % of the resouces. Also included:

- 2 I2C interfcaes

- 48 MHz oscillator

- 10 kHz oscillator

- IR TX/RX

- 3x 24 mA, 1x 100 mA, 1x 400 mA LED driver

- up to 10 I/O lines, 5 of those are open drain only

I didn't have any prior FPGA experience but this thing lowered the entry barrier enough for me to give it try. I managed to implement various blinkys, an SPI slave and a WS2812B driver:

There's an arduino library that configures dipsy over SPI, with a configuration stored in a plain C array. No further programming hardware required. The final design is planned to include a configuration flash chip as well.

Regards

Christoph