Hello,

I need some help to configure the FlexTimer module for this particular scenario:

I need to drive some power MOSFETs (H-bridge configuration) using PWM signals with unipolar modulation scheme, to generate a high power AC signal (50 Hz).

I need two independent output signals (one for each H-bridge legs) as I have a separate hw circuit to get the complementary signals with inserted dead time.

Let's presume the switching frequency is 10 kHz and the modulating frequency is 50 Hz.

The H-bridge should be driven like that:

During a 10 ms interval (50 Hz half wave), one leg will be tied to ground (PWM duty-cycle = 0) while the other one will be driven with a variable duty-cycle PWM signal (100 steps x 100 us = 10 ms).

After every 10 ms cycle, the PWM signals have to be switched (the first one will output variable duty-cycle PWM while the second one will generate a steady signal (duty-cycle = 0)).

The duty cycle value should be read from a sine wave look-up table (100 steps).

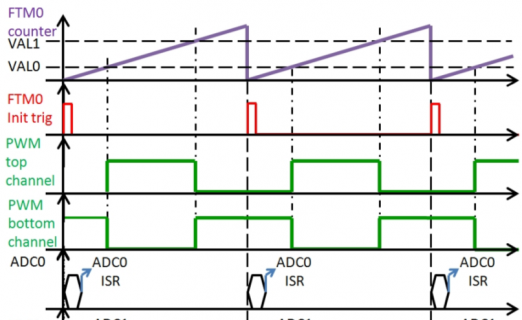

Every time the timer is restarting (overflow), I need it to fire up an ISR to do the rest of stuff (ADC readings, duty-cycle correction, serial communication).

The FTM channels should be edge-aligned.

So I need the following settings for the FTM(0):

(1) set the FTM frequency to 10 kHz

(2) define two PWM outputs, edge aligned

(3) fire up an ISR every 100 us (timer overflow)

Inside that ISR:

(4) set the next pulse duty-cycle value (from the look-up table)

(5) (after 100 iterations) switch the PWM signals output

Could someone write a simple sketch to start with? I really don't know how to manage steps (3) to (5).

I don't want to put anything else in the main loop() or to use any other interrupts. I want the PWM signals to be as jitter-free as possible.

Thank you very much for your time.

I need some help to configure the FlexTimer module for this particular scenario:

I need to drive some power MOSFETs (H-bridge configuration) using PWM signals with unipolar modulation scheme, to generate a high power AC signal (50 Hz).

I need two independent output signals (one for each H-bridge legs) as I have a separate hw circuit to get the complementary signals with inserted dead time.

Let's presume the switching frequency is 10 kHz and the modulating frequency is 50 Hz.

The H-bridge should be driven like that:

During a 10 ms interval (50 Hz half wave), one leg will be tied to ground (PWM duty-cycle = 0) while the other one will be driven with a variable duty-cycle PWM signal (100 steps x 100 us = 10 ms).

After every 10 ms cycle, the PWM signals have to be switched (the first one will output variable duty-cycle PWM while the second one will generate a steady signal (duty-cycle = 0)).

The duty cycle value should be read from a sine wave look-up table (100 steps).

Every time the timer is restarting (overflow), I need it to fire up an ISR to do the rest of stuff (ADC readings, duty-cycle correction, serial communication).

The FTM channels should be edge-aligned.

So I need the following settings for the FTM(0):

(1) set the FTM frequency to 10 kHz

(2) define two PWM outputs, edge aligned

(3) fire up an ISR every 100 us (timer overflow)

Inside that ISR:

(4) set the next pulse duty-cycle value (from the look-up table)

(5) (after 100 iterations) switch the PWM signals output

Could someone write a simple sketch to start with? I really don't know how to manage steps (3) to (5).

I don't want to put anything else in the main loop() or to use any other interrupts. I want the PWM signals to be as jitter-free as possible.

Thank you very much for your time.