EEPROM write testing: My thought was to test the various EEPROM Functions: read(),write(),update(),get(),put(),EEPROM[] - and of course test the access across boundaries, I skipped update() since the code reads and tests before writes as I saw it in all cases.

Allowing for the need of the pending drop out of HSRUN for EEPROM access - I tested at 96 MHz. Good news NO READ WRITE ERRORS in testing.

Starting with the Manitou sketch meant to confirm timing - I ended up with a master loop of 25 passes writing 164 bytes - so the last bytes four give access errors.

The first 50 bytes are char arrays of 16,8,4,2,9,7,3,1 written in that order using put(), the next 50 bytes the 1 byte is written first, then the rest skipping the last one byte - so if it wasn't odd the first time - it is the second. [Of course as soon as I write that 163 is prime what a great multiplier.] Then a simple write of 32 bytes EEPROM[] array style, then 32 byte written with a one byte write.

So every byte gets a repeatable value - the offset into the block of 164 bytes PLUS a fixed test value for that run.

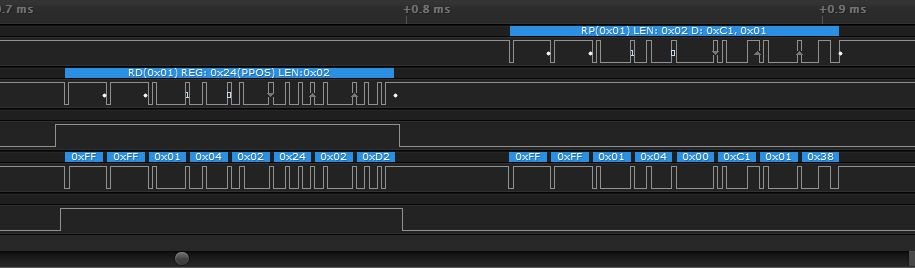

Two observations: Some blocks take much longer to write with a new value 1,470,077 .vs. 52,954 micros.

Second: In some cases the second write times indicate that the unchanged value caused 'no write' with 171 micros, others are slower at 3116 us, some actually take really long at 1,051,167 us. The number of some it seems is HALF - yep every other one - if anyone has a clue let me know as I hope to look at the code a bit.

Will post a sketch soon - I just have to try the 163 byte blocks. I also need to format the output as CSV so it can be table ordered and the boundaries better seen.

<EDIT>: I got my test refined - the write times are uniform - the problems were in my code. Will post when high HSRUN EEPROM access is released.