Hi All.

So, I'm embarking on a project where I will attempt to use this TI Chip:

http://www.ti.com/product/DIR9001/description

to decode an optical TOSLINK input and send the audio samples to the I2S Receiver of a Teensy 3.x for use by the Audio Library (namely FFT).

The Teensy's I2S Receiver will have to be in slave mode so that the DIR9001 can supply the bit clock and frame sync synchronous to the original sample rate of the TOSLINK input.

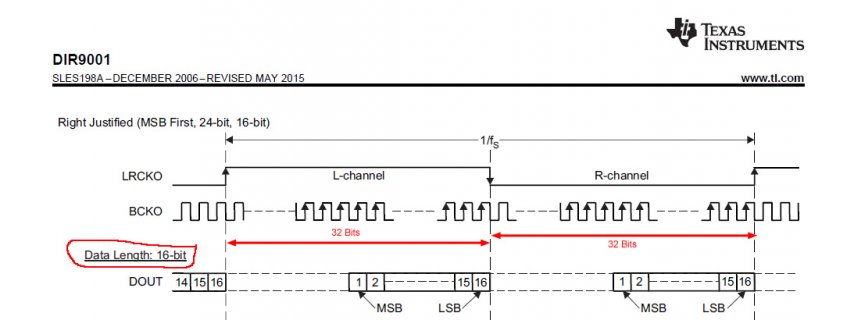

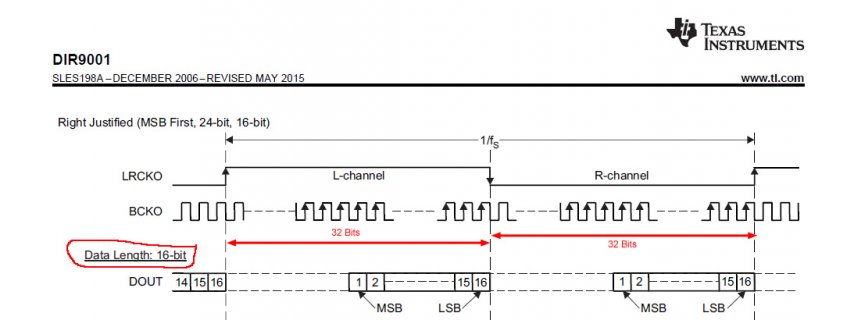

The only hitch I see is that the TI part has a fixed frame size of 2 words (Left and Right channels) and a fixed word size of 32 bits (i.e. 64 bits per frame). Knowing that the Teensy Audio Library operates on 16 bit samples, I've identified the settings in the TI chip to select 16 bit right-justified data in the 32 bit Left and Right channel locations:

I've also gone through the MK20DX256 datasheet and identified the register settings necessary to support slave mode and 2 x 32 bit words (64 bit frame).

My only concern now is will the I2S Input, AudioConnection, and other facilities of the Audio Library properly pull the 16 bit samples from the lower 2 bytes of each 32 bit sample word. I'm a decent C coder, but don't know C++. So, I get pretty lost looking at the Library source code to find the answer to this question.

Sorry for the long-winded post. Hope that someone out there who's smarter than me can provide some guidance on this question.

Thanks.

So, I'm embarking on a project where I will attempt to use this TI Chip:

http://www.ti.com/product/DIR9001/description

to decode an optical TOSLINK input and send the audio samples to the I2S Receiver of a Teensy 3.x for use by the Audio Library (namely FFT).

The Teensy's I2S Receiver will have to be in slave mode so that the DIR9001 can supply the bit clock and frame sync synchronous to the original sample rate of the TOSLINK input.

The only hitch I see is that the TI part has a fixed frame size of 2 words (Left and Right channels) and a fixed word size of 32 bits (i.e. 64 bits per frame). Knowing that the Teensy Audio Library operates on 16 bit samples, I've identified the settings in the TI chip to select 16 bit right-justified data in the 32 bit Left and Right channel locations:

I've also gone through the MK20DX256 datasheet and identified the register settings necessary to support slave mode and 2 x 32 bit words (64 bit frame).

My only concern now is will the I2S Input, AudioConnection, and other facilities of the Audio Library properly pull the 16 bit samples from the lower 2 bytes of each 32 bit sample word. I'm a decent C coder, but don't know C++. So, I get pretty lost looking at the Library source code to find the answer to this question.

Sorry for the long-winded post. Hope that someone out there who's smarter than me can provide some guidance on this question.

Thanks.

Last edited: