TelephoneBill

Well-known member

Looking for a little guidance on interrupt service routine timing...

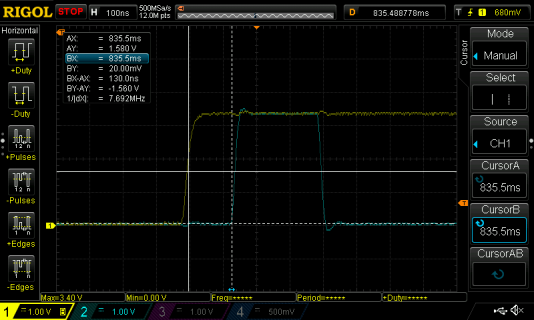

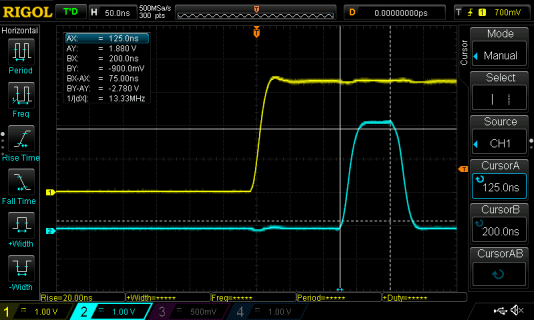

I want to use an FTM timer to compare two positive going edge signals (repeating) on two input pins configured as CH0 and CH1. I am concerned about the latency which exists from the instant of the rising edge to the instant that the first line of code executes in an associated ISR routine.

From memory, I think the latency is about 2 uSec for Teensy 3.1 running at 120 MHz. Can anyone confirm this? What about Teensy 3.6 running at 240 MHz - how long is this likely to be?

I'm also puzzled why it should take what seems to be such a long time for just dumping registers on the stack - 2 uSecs seems a lot of clock cycles.

Is there any way to speed this up?

Thanks for any info/confirmation of timing.

I want to use an FTM timer to compare two positive going edge signals (repeating) on two input pins configured as CH0 and CH1. I am concerned about the latency which exists from the instant of the rising edge to the instant that the first line of code executes in an associated ISR routine.

From memory, I think the latency is about 2 uSec for Teensy 3.1 running at 120 MHz. Can anyone confirm this? What about Teensy 3.6 running at 240 MHz - how long is this likely to be?

I'm also puzzled why it should take what seems to be such a long time for just dumping registers on the stack - 2 uSecs seems a lot of clock cycles.

Is there any way to speed this up?

Thanks for any info/confirmation of timing.