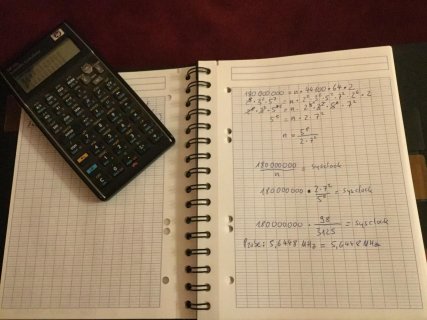

What is the fastest way to calculate I2S FRACT & DIVIDE values for a given F_PLL and Samplefreq?

For a new project, I need to calculate them "live", at runtime.

Edit:

For debugging, i needed the opposite way.

Perhaps it's useful for others, when fiddling with I2S - this codes calculates the samplefrequency from the I2S settings (works with all existing I2s outputs form the audiolib):

.. and now i need a fast way for the other direction

For a new project, I need to calculate them "live", at runtime.

Edit:

For debugging, i needed the opposite way.

Perhaps it's useful for others, when fiddling with I2S - this codes calculates the samplefrequency from the I2S settings (works with all existing I2s outputs form the audiolib):

Code:

if ((SIM_SCGC6 & SIM_SCGC6_I2S == SIM_SCGC6_I2S)) {

Serial.println("I2S enabled");

int fract = (I2S0_MDR >> 12) & 0xff;

int divide = I2S0_MDR & 0xfff;

int src = (I2S0_MCR >> 24) & 0x03;

double mclk = ((src == 3)? F_PLL : F_BUS) * (double)(fract + 1) / (double)(divide + 1);

int bitclockdiv = I2S0_TCR2 & 0xff;

int framesize = ((I2S0_TCR4 >> 16) & 0x0f) + 1;

int word0width = ((I2S0_TCR5 >> 24) & 0x1f) + 1;

int wordnwidth = ((I2S0_TCR5 >> 16) & 0x1f) + 1;

double samplerate = (mclk / ((bitclockdiv + 1) * 2)) / (word0width + wordnwidth * (framesize - 1 ));

#if 1

Serial.print("MCLK: ");

Serial.println(mclk);

Serial.print("FRAMESIZE: ");

Serial.println(framesize);

Serial.print("WORDWIDTH: ");

Serial.println(word0width);

Serial.println(wordnwidth);

Serial.print("FRAMELENGTH: ");

Serial.println( (word0width + wordnwidth * (framesize - 1 )));

Serial.print("SAMPLERATE: ");

Serial.println( samplerate, 4 );

#endif

}.. and now i need a fast way for the other direction