PaulStoffregen

Well-known member

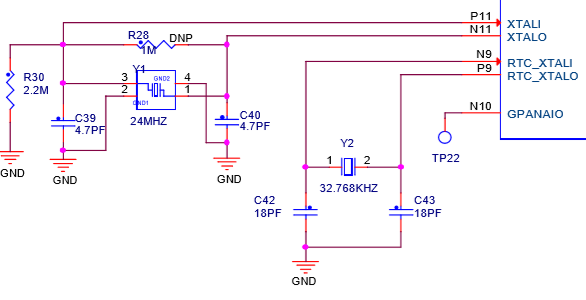

Both of those files seem to say the RTC oscillator should need smaller capacitors, though neither document seem to be very specific about the crystal specs.

Test results I'm seeing here seem to show nearly ideal frequency 12 pF on the 24 MHz crystal and 20 pF on the 32 kHz crystal.

I just swapped out the 13 pF capacitors from the worst performing RTC, which had +58 ppm error in the first 4 min after powerup. With 20 pF caps (and some rosin-based flux still on the board) I'm now seeing about +4.5 ppm error. Going to let this one run an hour or so to check after warmup, but it's already slowed by about 0.5 ppm while writing this message.

Test results I'm seeing here seem to show nearly ideal frequency 12 pF on the 24 MHz crystal and 20 pF on the 32 kHz crystal.

I just swapped out the 13 pF capacitors from the worst performing RTC, which had +58 ppm error in the first 4 min after powerup. With 20 pF caps (and some rosin-based flux still on the board) I'm now seeing about +4.5 ppm error. Going to let this one run an hour or so to check after warmup, but it's already slowed by about 0.5 ppm while writing this message.