Hi,

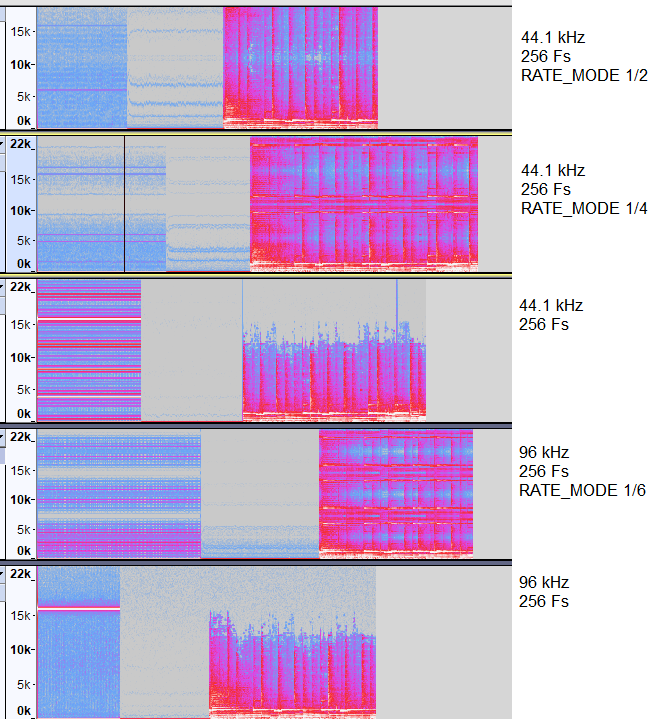

Just by chance I see you have been testing different setups to change the samplerate, have you done any further work on this ? One of odd things your spectrum graphs show is that with a SR of 44.1Khz (default for SGTL5000 on teensy) and 256Fs (also default) the spectrum for the 15Khz signal is rather "full" with many other signals. Did you use the same signalstrength for the 96Khz&256Fs ?

regards

Cor

Hi. I haven't done further research on this as I have switched to Frank B's suggested

AdioTiming library as method to change sample rate.

I can't remember now if I realiced about what you comment on the 44.1Khz - 256Fs spectrum. I guess it was due to some disstorsion in the signal, as sometimes I get unwanted noise in my recordings.

As far as I can remember I used the same signalstrength for all tests.

I have tried to replicate the test again, but now I am getting a lot of noise when I change the chip parameters. If I have time to continue working on it I'll post here any interesting output I may get.

One thing I am still not sure about is whether the SGTL5000 has an anti-aliasing filter or not. Neither in the the documentation nor the manufacturer forums there I have found any reference about it. Nevertheless Paul

said he could conclude with some tests that the filter is present in the chip. I tried to test it myself, but my results where not conclusive, although my aproach was quite rudimentary, as I don't have a signal generator.

In you or anyone is interested, this are the different values I used in the control_sgtl5000.cpp file:

write(CHIP_CLK_CTRL, 0x0004); // 44.1 kHz, 256*Fs --> 44100 Hz (default)

write(CHIP_CLK_CTRL, 0x0014); // 44.1 kHz, 256*Fs, RATE_MODE 1/2 of the SYS_FS rate --> 22050 Hz

write(CHIP_CLK_CTRL, 0x0024); // 44.1 kHz, 256*Fs, RATE_MODE 1/4 of the SYS_FS rate --> 11025 Hz

write(CHIP_CLK_CTRL, 0x0034); // 44.1 kHz, 256*Fs, RATE_MODE 1/6 of the SYS_FS rate --> 7350 Hz

write(CHIP_CLK_CTRL, 0x000C); // 96 kHz, 256*Fs --> 96000 Hz

write(CHIP_CLK_CTRL, 0x003C); // 96 kHz, 256*Fs, RATE_MODE 1/6 of the SYS_FS rate --> 19000 Hz

write(CHIP_CLK_CTRL, 0x0018); // 48 kHz, 256*Fs, RATE_MODE 1/2 of the SYS_FS rate --> 24000 Hz

BTW, cool project that batdetector.