Ishkabbible

Member

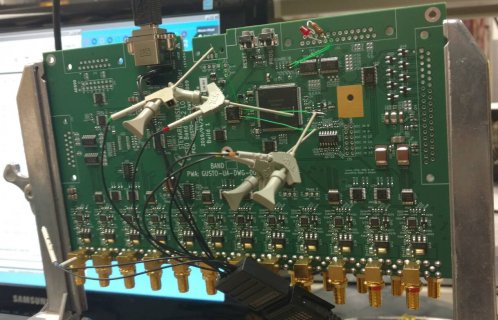

I am sending a couple of Teensys to the edge of space. Unfortunately, after thermal cycling a PJRC Teensy 3.6 I found cracks in some of the solder balls, so I have to go with a custom design using the QFP versions of the K66 and MKL04 chips.

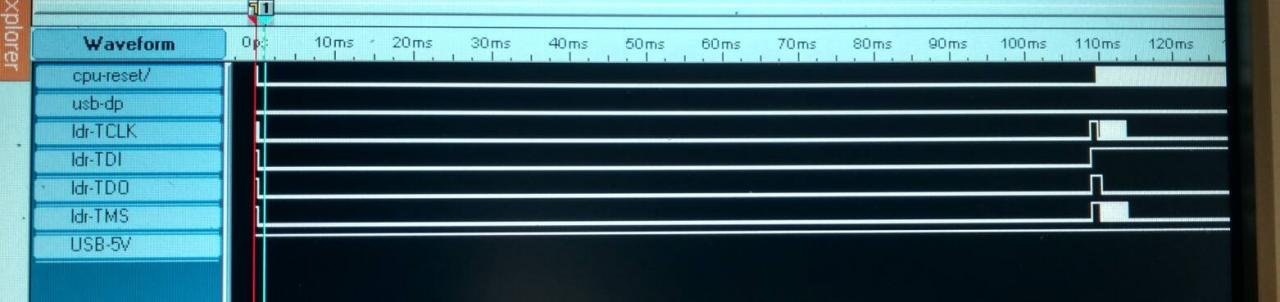

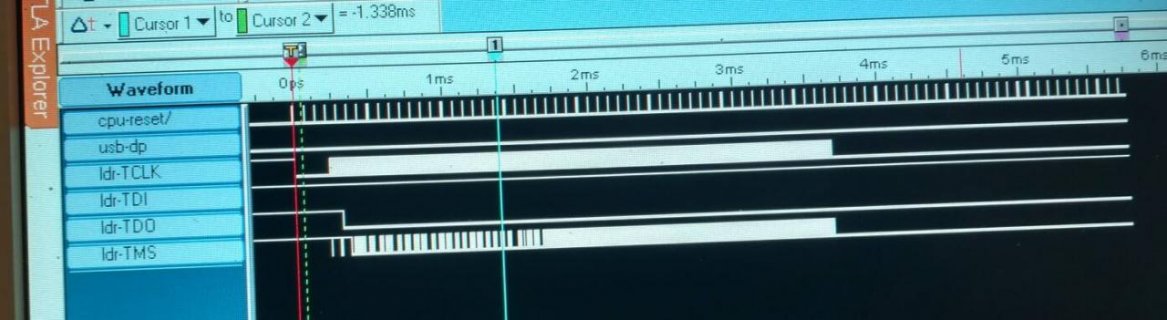

However, when I power up the board, the PC does not recognize the board. Putting a scope on the USB data pins shows there is nothing happening. With the logic analyzer on the JTAG lines between the MKL04 and the K66, I see the MKL04 banging away on TCLK and TMS for almost 4mS, but nothing on the TDI or TDO lines. While this is happening, the RESET_B line is also pulsing positive with about a 70uS cadence.

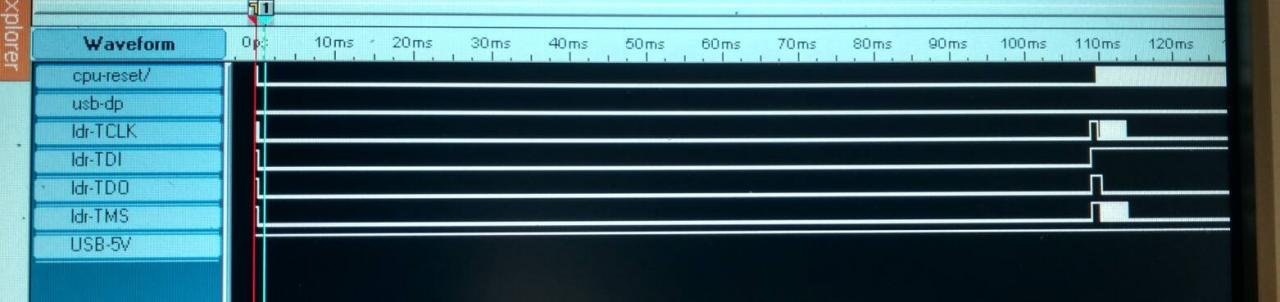

This shows the grand sweep of time from when the +5 comes up

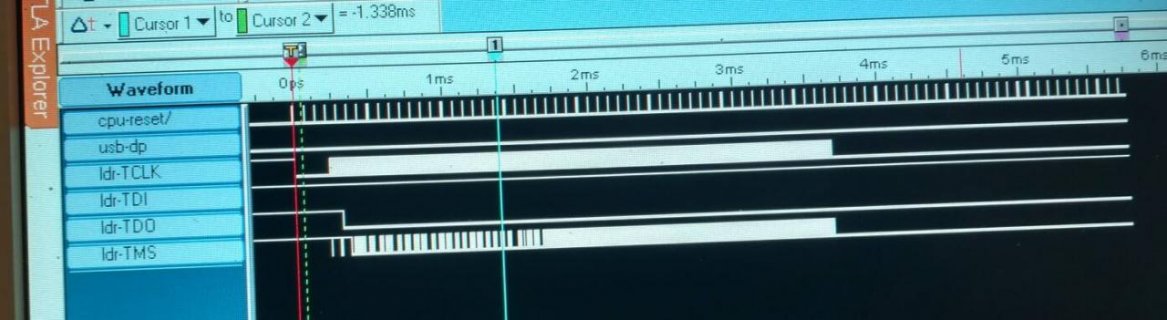

Zooming in on the activity on TCLK and TMS

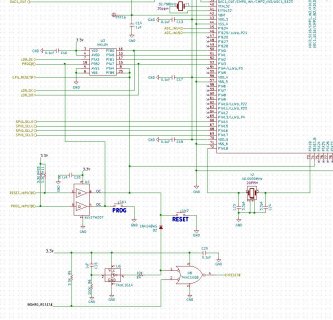

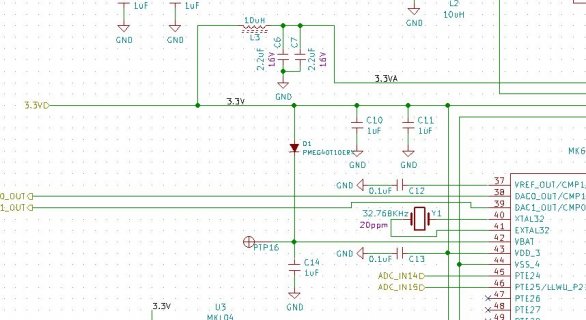

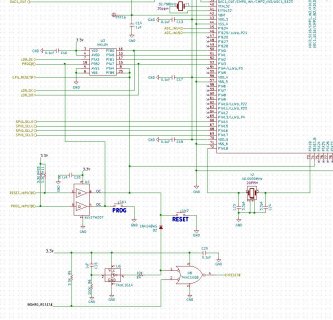

I can't get to those signals on my real Teensy3.6 to do a comparison. Here is the pertinent part of the schematic. The POR circuit formed by U5 and U6 is to reset off-board peripherals. The 10K R4 prevents this circuit from pulling RESET_B high through D2, but allows RESET_B or BOARD_RESET# to force the peripherals into reset. The open drain driver U4 allows the main data computer on the other end of the USB cable to reprogram this board in flight. The CPU chip is a MK66FX1M0VLQ18 purchased from Digikey (568-13334-ND).

Note that all of the JTAG lines DO change state at various times during the boot sequence, so there are no stuck lines. I have verified a nice 16MHz sine wave on both sides of the crystal. The 3.3V power is nice and stable at 3.299V, and current draw is as expected.

Anyone see anything I've missed?

However, when I power up the board, the PC does not recognize the board. Putting a scope on the USB data pins shows there is nothing happening. With the logic analyzer on the JTAG lines between the MKL04 and the K66, I see the MKL04 banging away on TCLK and TMS for almost 4mS, but nothing on the TDI or TDO lines. While this is happening, the RESET_B line is also pulsing positive with about a 70uS cadence.

This shows the grand sweep of time from when the +5 comes up

Zooming in on the activity on TCLK and TMS

I can't get to those signals on my real Teensy3.6 to do a comparison. Here is the pertinent part of the schematic. The POR circuit formed by U5 and U6 is to reset off-board peripherals. The 10K R4 prevents this circuit from pulling RESET_B high through D2, but allows RESET_B or BOARD_RESET# to force the peripherals into reset. The open drain driver U4 allows the main data computer on the other end of the USB cable to reprogram this board in flight. The CPU chip is a MK66FX1M0VLQ18 purchased from Digikey (568-13334-ND).

Note that all of the JTAG lines DO change state at various times during the boot sequence, so there are no stuck lines. I have verified a nice 16MHz sine wave on both sides of the crystal. The 3.3V power is nice and stable at 3.299V, and current draw is as expected.

Anyone see anything I've missed?