TelephoneBill

Well-known member

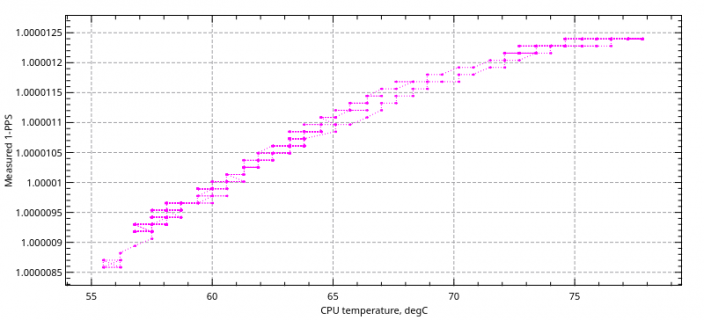

When measuring the output frequency of a QTIMER on a T4, I found it to be 5ppm slow on the theoretical value. This will be attributable to the 24 MHz oscillator also being 5ppm slow (within spec and temperature related).

To try compensate, I have been experimenting with ideas to FINE control the T4 peripheral clock. I did try adjust the bias current for XTALOSC24M_MISC0, but I could not see any appreciable osc frequency change over the programmable range. Certainly not of ppm size.

So the next idea is to synthesize the output frequency by changing the COMPARE value at infrequent intervals, in order to "drop" a 6.7 nS (one 150 MHz clock pulse) period, and thereby speed up the QTIMER output by a predictably small amount. But this is a bit of a coarse method.

But before I take this approach, I wondered if there was any (possibly non documented) ways to "nudge" the 150 MHz peripheral clock frequency by fine amounts?

Lastly, where can I download a spec from the web for the 24 MHz crystal module? Thanks for any info...

To try compensate, I have been experimenting with ideas to FINE control the T4 peripheral clock. I did try adjust the bias current for XTALOSC24M_MISC0, but I could not see any appreciable osc frequency change over the programmable range. Certainly not of ppm size.

So the next idea is to synthesize the output frequency by changing the COMPARE value at infrequent intervals, in order to "drop" a 6.7 nS (one 150 MHz clock pulse) period, and thereby speed up the QTIMER output by a predictably small amount. But this is a bit of a coarse method.

But before I take this approach, I wondered if there was any (possibly non documented) ways to "nudge" the 150 MHz peripheral clock frequency by fine amounts?

Lastly, where can I download a spec from the web for the 24 MHz crystal module? Thanks for any info...