defragster

Senior Member+

@luni - re #2:

back to short off topic - clock speed … as noted by KurtE - try 200 not 300 MHz - Using 200 MHz: if (div_ipg > 3) div_ipg = 3;

My test now gets all the printed contents the DMA the code does, and improves access from 4 clocks to 3 clocks as written. Most of 32000 are done in 2 clocks : CC@2=27307 - only 10% more than at 150 MHz that showed CC@2=24688

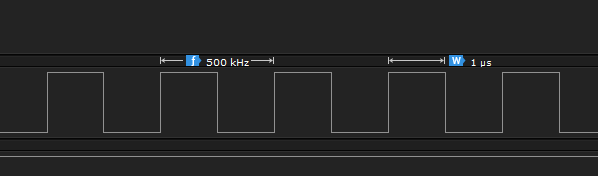

Code I first see above p#7 doesn't have the "dsb": can you locate the code of interest and assure it has that and retest?Making the timer faster is one thing, but you should really look at the load this generates. Currently the T4 gets already overloaded by 4 PITs just flipping pins at about 300kHz. So, making it possibly faster without solving the load issue might generate more issues than it solves. Further up in this thread I showed measurements with the TMRs since they run on 150MHz. One TMR overloads the T4 (can't even blink the LED) at about 4MHz, didn't do experiments with more timers running in parallel so far.

back to short off topic - clock speed … as noted by KurtE - try 200 not 300 MHz - Using 200 MHz: if (div_ipg > 3) div_ipg = 3;

Code:

Avg CycCnt for 32000 is 3.009719

CC@0=1 CC@2=27307 CC@3=1 CC@4=2158 CC@7=2 CC@8=539 CC@9=1 CC@10=539 CC@12=539 CC@18=912 CC@29=1My test now gets all the printed contents the DMA the code does, and improves access from 4 clocks to 3 clocks as written. Most of 32000 are done in 2 clocks : CC@2=27307 - only 10% more than at 150 MHz that showed CC@2=24688