Hello Friends,

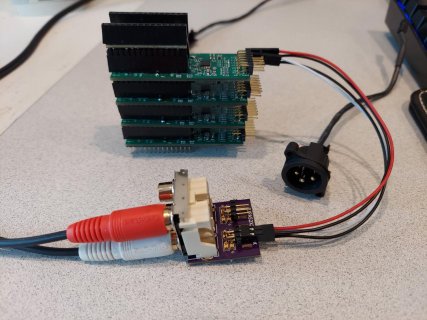

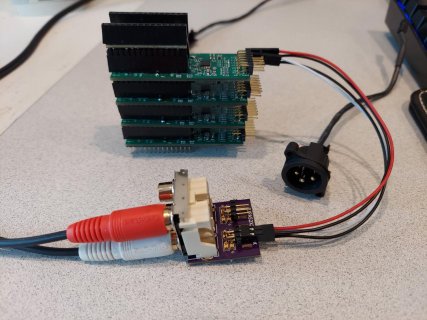

I've pretty much completed the drivers for both the DAC and the ADC. My first major test was to see if I could get 4 DACs hooked up to get 8 channels out. I have succeeded to make it work!

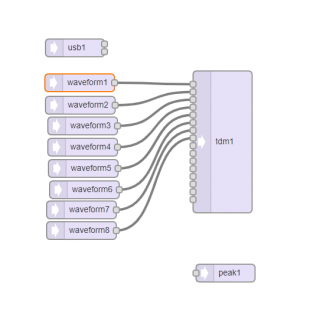

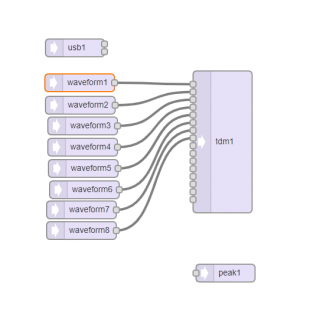

I created a USBPassthrough_TDM sketch, and a WaveFormTest_TDM sketch that is used in the following video. In the beginning of the video I'm showing the USB passthrough, and then towards the end I show that each of the outputs are playing different frequency wave forms.

Here's a video demo.

Upon initial testing, the I2C was jamming up. I could successfully communicate with 3 of the devices at one time, but the fourth one would break the I2C. I had to enable two (of the four) "PU_EN" (pull-up enable) jumpers so we have two 2.2k pullups on the I2C lines. Once I did this I can successfully communicate with all 4 at the same time. I'm not sure why it works with 2 pullups enabled, and not just one. If you have any logic to share with me about this it would help me, so that I can ensure that the design is robust. Should I change the values? is there something that you can imagine is happening?

Up next: I'll do a similar test with my ADC module!

I've pretty much completed the drivers for both the DAC and the ADC. My first major test was to see if I could get 4 DACs hooked up to get 8 channels out. I have succeeded to make it work!

I created a USBPassthrough_TDM sketch, and a WaveFormTest_TDM sketch that is used in the following video. In the beginning of the video I'm showing the USB passthrough, and then towards the end I show that each of the outputs are playing different frequency wave forms.

Here's a video demo.

Upon initial testing, the I2C was jamming up. I could successfully communicate with 3 of the devices at one time, but the fourth one would break the I2C. I had to enable two (of the four) "PU_EN" (pull-up enable) jumpers so we have two 2.2k pullups on the I2C lines. Once I did this I can successfully communicate with all 4 at the same time. I'm not sure why it works with 2 pullups enabled, and not just one. If you have any logic to share with me about this it would help me, so that I can ensure that the design is robust. Should I change the values? is there something that you can imagine is happening?

Up next: I'll do a similar test with my ADC module!