PaulStoffregen

Well-known member

Edit: Teensy 4.1 was released on May 11, 2020. The beta test is finished. You can buy Teensy 4.1 now.

https://www.pjrc.com/store/teensy41.html

We will soon begin a public beta test for Teensy 4.1.

At this time, PJRC would like to offer free Teensy 4.1 boards to the following people:

AdmiralCrunch, adrianfreed, Arctic_Eddie, bicycleguy, Bill Greiman, Blackaddr, blackketter, bmillier, bossredman, brendanmatkin, brtaylor, chipaudette, Chris O., christoph, CorBee, crees, danixdj, DaQue, DD4WH, defragster, DerekR, Don Kelly, Donziboy2, duff, easone, edrummer, Elmue, el_supremo, ETMoody3, flashburn, Frank B, Gadget999, Gerrit, gfvalvo, Gibbedy, GremlinWrangler, hubbe, HWGuy, ikravets, JBeale, jbliesener, jcarruthers, Jean-Marc, jeffmhopkins, jimmayhugh, john-mike, jonr, Jp3141, jwatte, Koromix, kriegsman, KrisKasprzak, KurtE, LenSamuelson, loglow, luni, manitou, markonian, Markus_L811, MichaelMeissner, MickMad, mjs513, mlu, mortonkopf, mxxx, Nantonos, neurofun, nlecaude, Nominal Animal, nox771, oddson, Paul Hesketh, PaulS, Pedvide, Pensive, pictographer, Pointy, potatotron, Po Ting, prickle, Projectitis, rcarr, RichardFerraro, shawn, sumotoy, tannewt, Teenfor3, TelephoneBill, tenkai, Theremingenieur, tni, tonton81, tubelab.com, turtle9er, urbanspaceman, visual_micro, vjmuzik, wangnick, Ward, Wayne, wcalvert, widdly, WMXZ, Wozzy, wwatson, XFer, xxxajk, yeahtuna

We've already sent early boards to 5 people on this list. Another 24 boards pre-production boards are available now, but there is a minor catch. These 24 boards have a mistake where one of the 3.3V pins and two GND pins aren't connected, due to an error in how the PCB panelization was done for this small pre-production batch. Otherwise, these 24 boards do work fine, you just can't use those 3 power pins.

Everyone on this list who does not receive a pre-production board will be offered a free Teensy 4.1 from the first production batch (which will have all power pins correct). If you're busy right now, or you'd just prefer to wait for the production batch, there is no need to do anything right now. We expect to release Teensy 4.1 sometime in May, so the wait will not be long...

If you'd like a pre-production Teensy 4.1 now, please email me directly (paul at pjrc dot com) with the magic words "I have time to beta test 4.1 and give feedback on the forum". Please mention your forum user name, and if sending from a different address than you've used for this forum, you must mention the email address registered to your forum account. There is no charge for these betas. PJRC will pay for shipping. If you're outside the USA and the carrier charges international tariff/vat/fees when the package arrives, you'll need to cover that cost. We can't pre-pay it from here.

EDIT: Photos are ok now that Teensy 4.1 has been released.

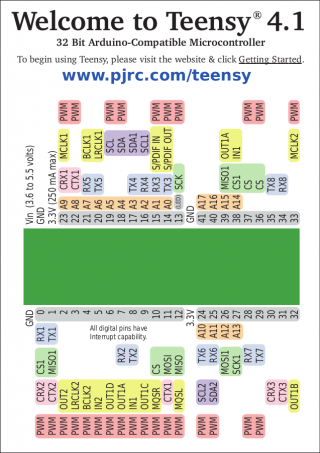

Maybe you're curious about the specs? Teensy 4.1 uses the same 600 MHz IMXRT1062 microcontroller as Teensy 4.0. The PCB is the larger 48-pin form factor (same as Teensy 3.5 & 3.6), which provides more I/O pins and easier access the SD card and USB Host. Teensy 4.1 has an 8 MB flash chip, an Ethernet PHY, and places on the bottom side to solder QSPI memory chips.

https://www.pjrc.com/store/teensy41.html

We will soon begin a public beta test for Teensy 4.1.

At this time, PJRC would like to offer free Teensy 4.1 boards to the following people:

AdmiralCrunch, adrianfreed, Arctic_Eddie, bicycleguy, Bill Greiman, Blackaddr, blackketter, bmillier, bossredman, brendanmatkin, brtaylor, chipaudette, Chris O., christoph, CorBee, crees, danixdj, DaQue, DD4WH, defragster, DerekR, Don Kelly, Donziboy2, duff, easone, edrummer, Elmue, el_supremo, ETMoody3, flashburn, Frank B, Gadget999, Gerrit, gfvalvo, Gibbedy, GremlinWrangler, hubbe, HWGuy, ikravets, JBeale, jbliesener, jcarruthers, Jean-Marc, jeffmhopkins, jimmayhugh, john-mike, jonr, Jp3141, jwatte, Koromix, kriegsman, KrisKasprzak, KurtE, LenSamuelson, loglow, luni, manitou, markonian, Markus_L811, MichaelMeissner, MickMad, mjs513, mlu, mortonkopf, mxxx, Nantonos, neurofun, nlecaude, Nominal Animal, nox771, oddson, Paul Hesketh, PaulS, Pedvide, Pensive, pictographer, Pointy, potatotron, Po Ting, prickle, Projectitis, rcarr, RichardFerraro, shawn, sumotoy, tannewt, Teenfor3, TelephoneBill, tenkai, Theremingenieur, tni, tonton81, tubelab.com, turtle9er, urbanspaceman, visual_micro, vjmuzik, wangnick, Ward, Wayne, wcalvert, widdly, WMXZ, Wozzy, wwatson, XFer, xxxajk, yeahtuna

We've already sent early boards to 5 people on this list. Another 24 boards pre-production boards are available now, but there is a minor catch. These 24 boards have a mistake where one of the 3.3V pins and two GND pins aren't connected, due to an error in how the PCB panelization was done for this small pre-production batch. Otherwise, these 24 boards do work fine, you just can't use those 3 power pins.

Everyone on this list who does not receive a pre-production board will be offered a free Teensy 4.1 from the first production batch (which will have all power pins correct). If you're busy right now, or you'd just prefer to wait for the production batch, there is no need to do anything right now. We expect to release Teensy 4.1 sometime in May, so the wait will not be long...

If you'd like a pre-production Teensy 4.1 now, please email me directly (paul at pjrc dot com) with the magic words "I have time to beta test 4.1 and give feedback on the forum". Please mention your forum user name, and if sending from a different address than you've used for this forum, you must mention the email address registered to your forum account. There is no charge for these betas. PJRC will pay for shipping. If you're outside the USA and the carrier charges international tariff/vat/fees when the package arrives, you'll need to cover that cost. We can't pre-pay it from here.

EDIT: Photos are ok now that Teensy 4.1 has been released.

Maybe you're curious about the specs? Teensy 4.1 uses the same 600 MHz IMXRT1062 microcontroller as Teensy 4.0. The PCB is the larger 48-pin form factor (same as Teensy 3.5 & 3.6), which provides more I/O pins and easier access the SD card and USB Host. Teensy 4.1 has an 8 MB flash chip, an Ethernet PHY, and places on the bottom side to solder QSPI memory chips.