Background: I'm looking at building a 8x8x8 RGB LED cube and have seen numerous tutorials. However, I prefer designing it myself, so that I understand how/why it works and gain valuable design experience, even though it takes more time, it's buggier, and it's significantly more difficult.

I want to use a teensy 4.1 to control 12 TLC5490s (I understand that the PJRC TLC5490 Library isn't compatible with the 4.1, so I will have to write my own driver similar to this one here: https://github.com/MaltWhiskey/LedCubeTeensy/blob/master/src/OctadecaTLC5940.h)

The TLC5490s daisy-chain together, but from what other people have said online, the LEDs start behaving erratically after the 6-10th one. I have seen two different options to solve this:

1. Use multiple SPI busses with DMA, so instead of 12 daisy-chained I have 4 or 6.

2. Use a non-inverting precision schmitt trigger (74HC7014D) every 3-6 TLC5490s to relay the signal

I'm currently leaning toward using multiple SPI ports because the 74HC7014D is limited to around 1MHZ, while the SPI bus can output at 5-30MHZ or so.

A few questions about using multiple SPI ports:

1. One example I saw was a Teensy 4.0 and 12 TLC5490s on 1 bus with the pins configured:

SPI0:

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK0 (pin 13)

SIN -> MOSI0 (pin 11)

a. Do I need to define MISO 0 or CS0 in the driver because the TLC5490 doesn't return data and doesn't have a Slave Select?

b. To scale this to three ports, should I reuse VPRG (6), GSCLK (7), BLANK (8) , and XLAT (9) for all three branches since I will write to all 12 TLC5490s at virtually the same time (EX1)? Or should I choose 4 different Digital/PWM ports for each SPI bus (EX2)?

EX1.

SPI 1

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK1 (pin 27)

SIN -> MOSI1 (pin 26)

SPI 2

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK1 (pin 45)

SIN -> MOSI1 (pin 43)

EX2

SPI 1

VPRG -> pin 2

GSCLK -> pin 3

BLANK -> pin 4

XLAT -> pin 5

SCLK -> SCK1 (pin 27)

SIN -> MOSI1 (pin 26)

SPI 2

VPRG -> pin 18

GSCLK -> pin 19

BLANK -> pin 22

XLAT -> pin 23

SCLK -> SCK1 (pin 45)

SIN -> MOSI1 (pin 43)

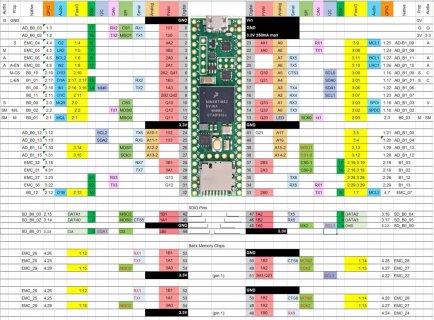

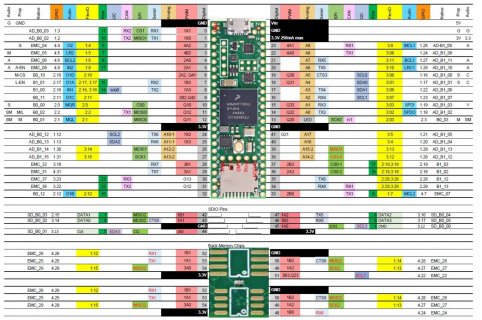

2. The Pinout diagrams of the Teensy 4.1 aren't exactly well labelled when it comes to pins 42 through 54 (SDIO pins and Back Memory Chips). The pinout diagram here (https://github.com/KurtE/TeensyDocuments/blob/master/Teensy4.1 Pins.pdf) shows the various functions of the pins, but doesn't link them to physical ports on the teensy.

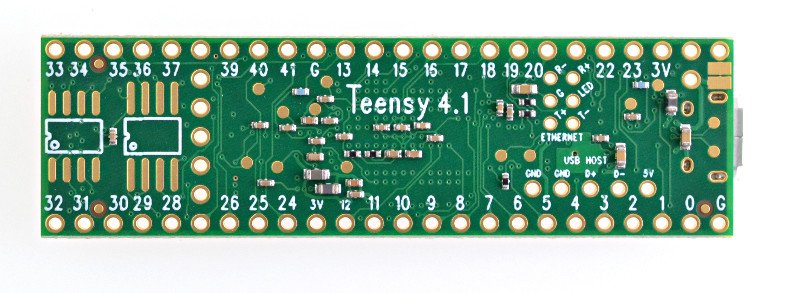

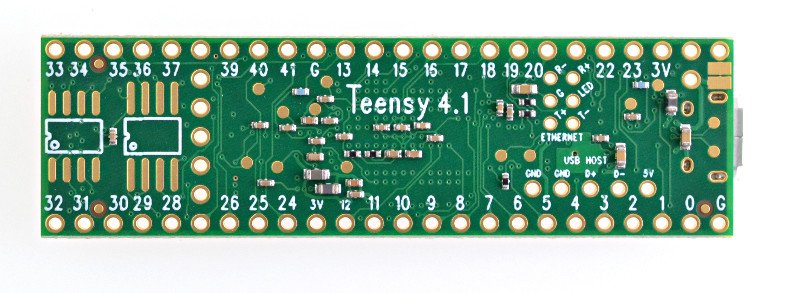

I've attached a photo of the back of the teensy 4.1. If someone code annotate the image or accurately describe, which pins are 42-54 in that orientation, especially the main and alternate sck2 and mosi2; it would be quite helpful.

Thank you!

I want to use a teensy 4.1 to control 12 TLC5490s (I understand that the PJRC TLC5490 Library isn't compatible with the 4.1, so I will have to write my own driver similar to this one here: https://github.com/MaltWhiskey/LedCubeTeensy/blob/master/src/OctadecaTLC5940.h)

The TLC5490s daisy-chain together, but from what other people have said online, the LEDs start behaving erratically after the 6-10th one. I have seen two different options to solve this:

1. Use multiple SPI busses with DMA, so instead of 12 daisy-chained I have 4 or 6.

2. Use a non-inverting precision schmitt trigger (74HC7014D) every 3-6 TLC5490s to relay the signal

I'm currently leaning toward using multiple SPI ports because the 74HC7014D is limited to around 1MHZ, while the SPI bus can output at 5-30MHZ or so.

A few questions about using multiple SPI ports:

1. One example I saw was a Teensy 4.0 and 12 TLC5490s on 1 bus with the pins configured:

SPI0:

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK0 (pin 13)

SIN -> MOSI0 (pin 11)

a. Do I need to define MISO 0 or CS0 in the driver because the TLC5490 doesn't return data and doesn't have a Slave Select?

b. To scale this to three ports, should I reuse VPRG (6), GSCLK (7), BLANK (8) , and XLAT (9) for all three branches since I will write to all 12 TLC5490s at virtually the same time (EX1)? Or should I choose 4 different Digital/PWM ports for each SPI bus (EX2)?

EX1.

SPI 1

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK1 (pin 27)

SIN -> MOSI1 (pin 26)

SPI 2

VPRG -> pin 6

GSCLK -> pin 7

BLANK -> pin 8

XLAT -> pin 9

SCLK -> SCK1 (pin 45)

SIN -> MOSI1 (pin 43)

EX2

SPI 1

VPRG -> pin 2

GSCLK -> pin 3

BLANK -> pin 4

XLAT -> pin 5

SCLK -> SCK1 (pin 27)

SIN -> MOSI1 (pin 26)

SPI 2

VPRG -> pin 18

GSCLK -> pin 19

BLANK -> pin 22

XLAT -> pin 23

SCLK -> SCK1 (pin 45)

SIN -> MOSI1 (pin 43)

2. The Pinout diagrams of the Teensy 4.1 aren't exactly well labelled when it comes to pins 42 through 54 (SDIO pins and Back Memory Chips). The pinout diagram here (https://github.com/KurtE/TeensyDocuments/blob/master/Teensy4.1 Pins.pdf) shows the various functions of the pins, but doesn't link them to physical ports on the teensy.

I've attached a photo of the back of the teensy 4.1. If someone code annotate the image or accurately describe, which pins are 42-54 in that orientation, especially the main and alternate sck2 and mosi2; it would be quite helpful.

Thank you!