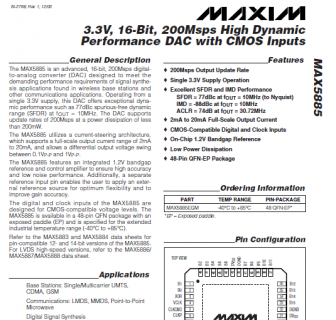

I attach the main page of the DAC datasheet.

A photo is not a link to the datasheet - but at least I know the part number now and dug it out.

The MAX5885 requires synchronous clock and data, so I don't see how what you are doing works with that - normally

the clocking would be quartz-stable and data is clocked every cycle from something like SDRAM. The chip has a 3.5

clock latency from data in to analog current output, so sending one clock pulse does nothing. Its not clear if it

can tolerate stop-start clocking either, perhaps I missed something in the datasheet though.

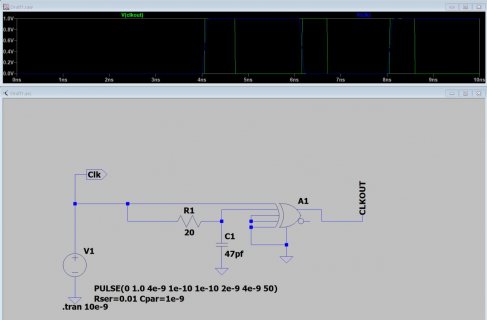

A 16 bit DAC needs ultra-low jitter to perform well at higher frequencies, since jitter directly translates to noise and

you are hoping for low noise or you wouldn't be needing 16 bits. Driving the clock pin asynchrnously will mean

the performance in terms of noise and SFDR will drop significantly.

I think you are better continuously clocking the DAC and using something like a 74LVC16374 to reclock the output

data to the DAC clock itself. However that chip's only spec'd to 120MHz or so, but its pretty easy to layout having 16 bussed

signals in and out.

I fully understand the subject of digital transmission lines in which I strongly agree with you, I am professionally dedicated to RF and Microwave engineering issues.

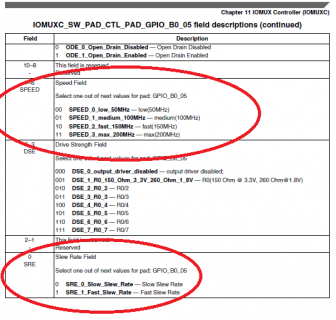

At the moment it is true that I do not comply at a practical level with the good practices for high speed circuits, but I repeat that I have looked at the conformation of the signals, including the delays of the parallel bits, the waveforms have sufficient spectral composition for an acceptable square signal and the rise times (10% - 90%) are less than 1 nS, thus deducing that the prototyping circuit is not the best for these time domains, when it manages to reduce the time consumption in sentences , I will begin to make a more suitable circuit design, with its reduced transmission lines and the corresponding ground planes.

My goal right now is to validate the TEENSY 4.1 + DAC capability in time response for the signal synthesizer project.

Some more information about how you are trying to use the T4.1 would be useful I think.