defragster

Senior Member+

https://forum.pjrc.com/threads/60021-Program-Flash-W25Q-speed

bootdata.c,

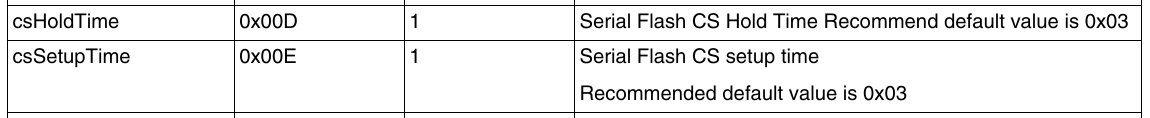

0x00030401, // lutCustomSeqEnable,serialClkFreq,sflashPadType,deviceType

Change that "3" to a higher number up to "8".

If want to test that for a benchmark or similar, you must keep in mind that the cache is enabled. It's not easy to test.

It plays a role for non-sequential random accesses. For data, for example.

I'd see it from the other side: Why put on a brake that is not necessary? This makes no sense.

Agreed that it is not quite right to artificially limit it - if testing show it stable at closer to SPEC speeds.

LittleFS will process some megabytes in a matter of seconds.

Test just done on QSPI chip did "Bytes read 219461632, written 49676288" in 3.27 minutes or 1,300,183 I/O Bytes/sec so the 32KB cache will only be of 'some' help, and a quick 'n'o Verify will drop the read back after write so it would almost never be in the same place twice for the cache to help.

So :: 0x00060401, // lutCustomSeqEnable,serialClkFreq,sflashPadType,deviceType

or :: 0x00080401, // lutCustomSeqEnable,serialClkFreq,sflashPadType,deviceType

Would change the speed from ? to ?? and ??.

- maybe it is in the link ... but ... time for Z's