You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Teensy 4.0 SCK speed?

- Thread starter GOHO

- Start date

- Status

- Not open for further replies.

defragster

Senior Member+

Hi, I want to use the Teensy 4.0 with Analogs LTC2314 ADC. In order to achieve the full 4.5msps I need a sck speed of 90mhz.

Can anyone tell me the max speed I could achieve on the 4.0 sck pin?

Thanks!

Been a while since something about the SPI clock went by - IIRC the clock could hit maybe 60 or 80 MHz.

YMMV - can't recall the device or thread that was posted on ... or how it was tested - other than requesting a speed and measuring the results for change.

KurtE

Senior Member+

If I remember correctly we setup the LPSPI clock in SPIClass::begin()

CCM_CBCMR = (CCM_CBCMR & ~(CCM_CBCMR_LPSPI_PODF_MASK | CCM_CBCMR_LPSPI_CLK_SEL_MASK)) |

CCM_CBCMR_LPSPI_PODF(2) | CCM_CBCMR_LPSPI_CLK_SEL(1); // pg 714

// CCM_CBCMR_LPSPI_PODF(6) | CCM_CBCMR_LPSPI_CLK_SEL(2); // pg 714

Which I believe says we wish to use the 720mhz clock CCM_CBCMR_LPSPI_CLK_SEL(1)

CCM_CBCMR_LPSPI_CLK_SEL(1)

And divide it by 3: CCM_CBCMR_LPSPI_CLK_SEL(2)

So 240mhz LPSPI clock

With this setup in beginTransaction you ask for 90mhz... 240mhz/90mhz

d=2 which may round to 0... So not sure if the speed generated will be 120mhz or 80mhz...

You can experiment to find out. Also one can much with the CCM_CBCMR setup to try to get different speeds...

CCM_CBCMR = (CCM_CBCMR & ~(CCM_CBCMR_LPSPI_PODF_MASK | CCM_CBCMR_LPSPI_CLK_SEL_MASK)) |

CCM_CBCMR_LPSPI_PODF(2) | CCM_CBCMR_LPSPI_CLK_SEL(1); // pg 714

// CCM_CBCMR_LPSPI_PODF(6) | CCM_CBCMR_LPSPI_CLK_SEL(2); // pg 714

Which I believe says we wish to use the 720mhz clock

And divide it by 3: CCM_CBCMR_LPSPI_CLK_SEL(2)

So 240mhz LPSPI clock

With this setup in beginTransaction you ask for 90mhz... 240mhz/90mhz

d=2 which may round to 0... So not sure if the speed generated will be 120mhz or 80mhz...

You can experiment to find out. Also one can much with the CCM_CBCMR setup to try to get different speeds...

PaulStoffregen

Well-known member

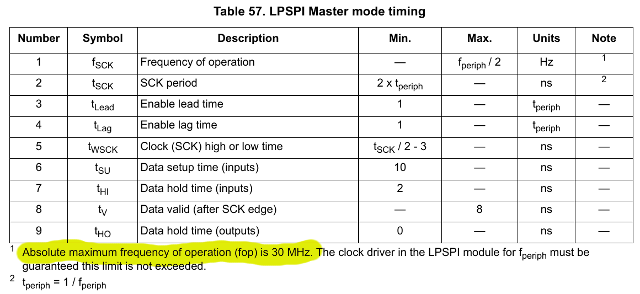

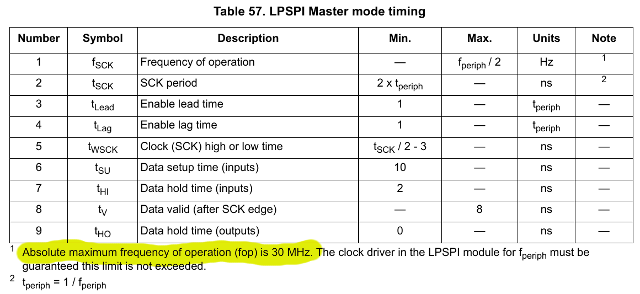

How fast the SPI port can actually work and how fast NXP officially specifies it to work are 2 different questions.

I'm sad to say the official word from NXP in the datasheet is only 30 MHz.

I've heard people say ILI9341 works with SPI clocks up to 60 MHz. Clearly NXP's spec is pretty conservative. But we also see that with CPU overclocking, where most chips will run at 960 MHz using a small heatsink, even though the official spec is only 600 MHz.

I'm sad to say the official word from NXP in the datasheet is only 30 MHz.

I've heard people say ILI9341 works with SPI clocks up to 60 MHz. Clearly NXP's spec is pretty conservative. But we also see that with CPU overclocking, where most chips will run at 960 MHz using a small heatsink, even though the official spec is only 600 MHz.

I remember we had it working with way more than 60MHZ., during the 4.0 beta test.

But I can't remember what speed it was, and I tested with an ILI9341 which may have been the limiting factor. And i did not have the right instruments to measure these speeds.

I can remember - in theory - there are even settings above 100MHz possible (which involves switching to an other PLL). I have no Idea if that would work, though.

I took a very brief look at the data sheet - seems that the chip is a bit picky about timings. That could also make it difficult. So I would first take a close look at the data sheet.

But I can't remember what speed it was, and I tested with an ILI9341 which may have been the limiting factor. And i did not have the right instruments to measure these speeds.

I can remember - in theory - there are even settings above 100MHz possible (which involves switching to an other PLL). I have no Idea if that would work, though.

I took a very brief look at the data sheet - seems that the chip is a bit picky about timings. That could also make it difficult. So I would first take a close look at the data sheet.

defragster

Senior Member+

Seems it was testing on the ILI9341 it went to 60 MHz with improved update and asking for more did not show faster completion - which then seemed like clock wasn't advancing as expected because the drawing IIRC was fine - just no faster. Only gauge here was the display rate - no clock testing.

Discussion seems like prior posts back when that was?

Discussion seems like prior posts back when that was?

- Status

- Not open for further replies.