Morning all (Still need coffee)

Will sink and Play... I am not sure if it is a good next approach, but I might see how well I can adapt the FlexIO code to maybe use some of the stuff in my FlexIO library. i.e. see how well it adapts.

Then maybe if for example 4 bits mode works, then I have all of the code in place to allow you to choose different ports/pins and it will take care of the configuration data...

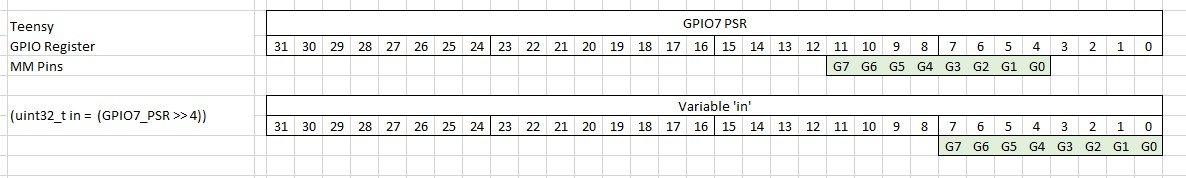

As for GPIO and reading in the 4 or 8 bits, with the MMOD board as you mentioned we are doing: uint32_t in = (GPIO7_PSR >> 4); // read all bits in parallel

With some of the GPIO code again as you showed the bits are not contiguous, so the code on T4 was doing something like:

Code:

uint16_t b = buffer[i] >> 18;

b = (b & 0x3) | ((b & 0x3f0) >> 2);

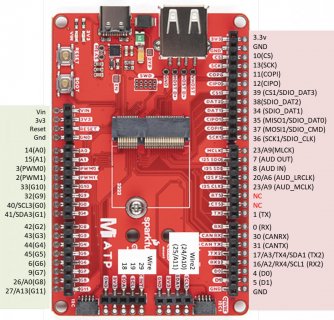

I thought I would mention that there is a 3rd setup, that on T4.1, if you are using the CSI pins:

Code:

1.22 17/A3 CSI_VSYNC

1.23 16/A2 CSI_HSYNC

1.24 22/A8 CSI_D9

1.25 23/A9 CSI_D8

1.26 20/A6 CSI_D7

1.27 21/A7 CSI_D6

1.28 38/A14 CSI_D5

1.29 39/A5 CSI_D4

1.30 26/A12 CSI_D3

1.31 27/A13 CSI_D2

You will notice that the 8 GPIO pins are in consecutive order at the top of register and in reverse order

So in this case I use: uint32_t in = __RBIT(GPIO6_PSR); // read all bits in parallel

Which reads in all of the bits and reverses them bit wise... so the 8 bits end up at the start of the uint32_t in the correct order...