Hi,

I currently working to a midi controller project based on Teensy 3.5. I try to connect 8 tft screens (this one base on ST7789 driver) using two hardware SPI ports from the teensy (so 4 screens by SPI port). To do so, I use "ST7789_t3" and "spi4teensy3" libraries. So far, I made a demo using my prototyping board and I don't understand the way the SCKL port is working.

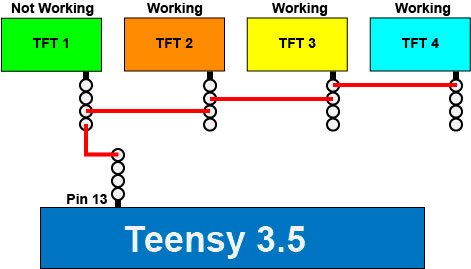

All the SPI pins works perfectly "daisy chained" which means that I connected the pin (CS, DC/RS, MOSI but not Reset - i use the autoreset function of the screen - and MISO - I don't use the SD port) from the teensy to the first screen, the first screen to the second one,... (T->1->2->3->4) but not the SCLK pin. If I do so, the first screen in the chain does not initialize even if the 3 remaining one are working correctly. if I disconnect the SCLK of the last screen (T->1->2->3), the first screen initializes but obviously I still miss one screen.

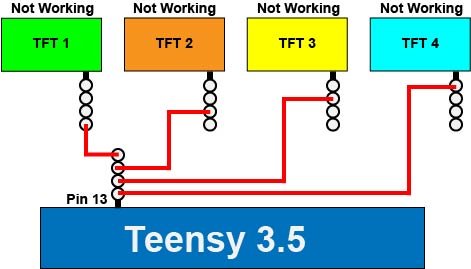

iedy to connect all the SCLK pins of the screen directly to the SCLK pin of the teensy (aka "parallel chain", T->1 // T->2 // T->3 // T->4), none of the screens was initialized. The only way to get the 4 screens working is a strange combination:

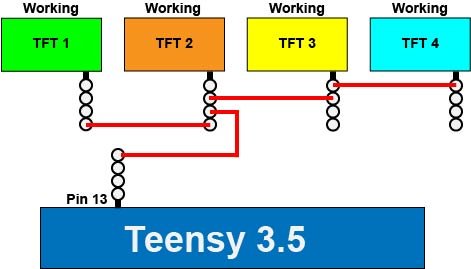

- I connect the teensy SCLK pin to the second screen

- I connect the SCLK pin of the second screen to the first and third one in parallel.

- I connect the last screen SCLK to the third one in daisy chained.

(so T->2->3->4 // 2->1)

This behaviour seems to be linked to loading effect but I don't understand it, especially knowing that each TFT screen use 74HC4050D chip to buffer all the pins so the loading should be quite low.

Obviously I tried to reduce the SPI clock (6000000 to 24000000), and even the functions setClockDivider() but no change so far.

I need now to design my PCB but as I don't understand the behaviour of the SPI Clock, I feel a little bit uncomfortable. Does someone understand it and could explain to me what is going on?

Thanks in advance.

I currently working to a midi controller project based on Teensy 3.5. I try to connect 8 tft screens (this one base on ST7789 driver) using two hardware SPI ports from the teensy (so 4 screens by SPI port). To do so, I use "ST7789_t3" and "spi4teensy3" libraries. So far, I made a demo using my prototyping board and I don't understand the way the SCKL port is working.

All the SPI pins works perfectly "daisy chained" which means that I connected the pin (CS, DC/RS, MOSI but not Reset - i use the autoreset function of the screen - and MISO - I don't use the SD port) from the teensy to the first screen, the first screen to the second one,... (T->1->2->3->4) but not the SCLK pin. If I do so, the first screen in the chain does not initialize even if the 3 remaining one are working correctly. if I disconnect the SCLK of the last screen (T->1->2->3), the first screen initializes but obviously I still miss one screen.

iedy to connect all the SCLK pins of the screen directly to the SCLK pin of the teensy (aka "parallel chain", T->1 // T->2 // T->3 // T->4), none of the screens was initialized. The only way to get the 4 screens working is a strange combination:

- I connect the teensy SCLK pin to the second screen

- I connect the SCLK pin of the second screen to the first and third one in parallel.

- I connect the last screen SCLK to the third one in daisy chained.

(so T->2->3->4 // 2->1)

This behaviour seems to be linked to loading effect but I don't understand it, especially knowing that each TFT screen use 74HC4050D chip to buffer all the pins so the loading should be quite low.

Obviously I tried to reduce the SPI clock (6000000 to 24000000), and even the functions setClockDivider() but no change so far.

I need now to design my PCB but as I don't understand the behaviour of the SPI Clock, I feel a little bit uncomfortable. Does someone understand it and could explain to me what is going on?

Thanks in advance.