You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Using TDA1543A with Teensy 4.0

- Thread starter layetri

- Start date

- Status

- Not open for further replies.

Hallo Frank,

Thanks. Tested your code and the sine looks fine on the oscilloscope.

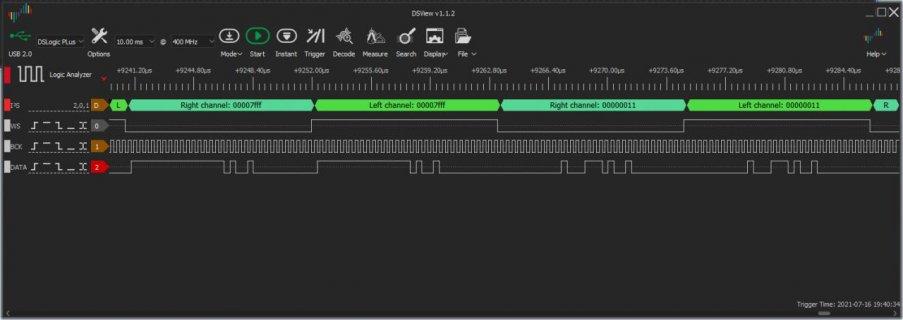

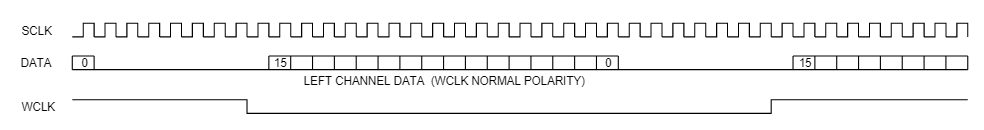

Hooked up the logic analyzer and saw this:

View attachment 25279

So apparently the TDA1543A needs japanese (2's-complement) data as 32+32 bits per sample? WS = 44.1 kHz, BCK = 2.84 MHz.

Paul

I've seen this format the first time.

After WS, it needs 7 dummy cycles (Pazis code set them to '1' - I removed that since it doesn't seem to be needed - see previous post), then 16 data bits, the rest gets ignored.

PaulS

Well-known member

PaulS

Well-known member

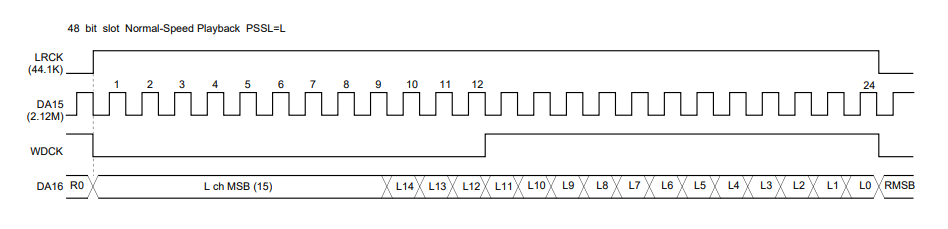

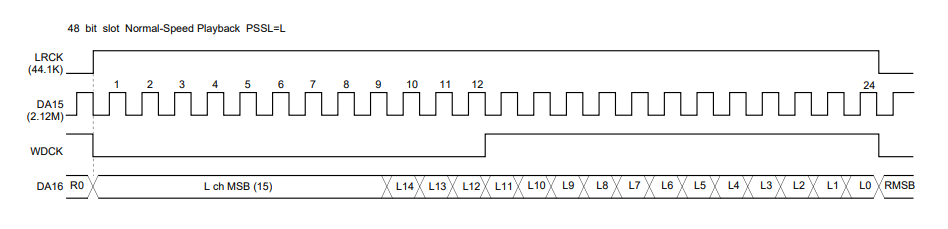

From the datasheet of the Sony CXD2500BQ [CD Digital Signal Processor] that was used in Marantz CD players and could drive a TDA1543A directly:

The chip outputs data at 48*LRCK rate [2.12 MHz]. The first 8 bits are ignored. And apparently the TDA1543A ignores bits >24.

The Philips SAA7345 signal processor, used in Philips CD players to drive the TDA1543A, does the same:

Paul

The chip outputs data at 48*LRCK rate [2.12 MHz]. The first 8 bits are ignored. And apparently the TDA1543A ignores bits >24.

The Philips SAA7345 signal processor, used in Philips CD players to drive the TDA1543A, does the same:

Paul

PaulS

Well-known member

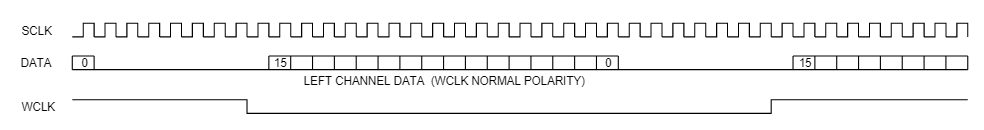

Thinking about it a bit longer, I think what the TDA1543A needs is a right-justified I2S signal. So the edge of the LRCK [aka WS] signals the end of the incoming left or right data.

That data can be 16 or 24 or 32 bit long [or 100 bits for that matter] - the TDA1543A just accepts the last 16 bits before the LRCK edge and discards all previous bits.

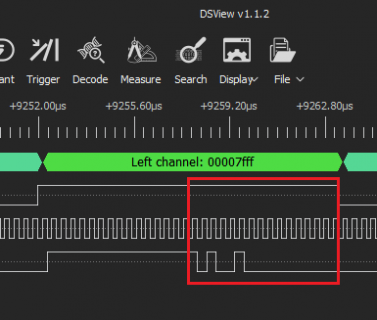

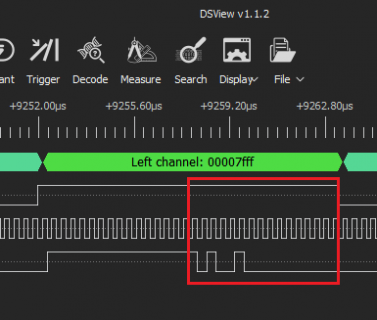

Having said that and looking at the logic analyzer snapshot: this means that the 8 least-significant bits of our digital sine word are seen as the 8 most-sigificant bits of the sine word since the last 8 bits before the LRCK bits are zero... Maybe the picture below makes it more clear. Is the TDA1543A only looking at the data in red rectangle?

I will check the actual analog signal in detail on the scope tomorrow. My brains are done for today...

Paul

That data can be 16 or 24 or 32 bit long [or 100 bits for that matter] - the TDA1543A just accepts the last 16 bits before the LRCK edge and discards all previous bits.

Having said that and looking at the logic analyzer snapshot: this means that the 8 least-significant bits of our digital sine word are seen as the 8 most-sigificant bits of the sine word since the last 8 bits before the LRCK bits are zero... Maybe the picture below makes it more clear. Is the TDA1543A only looking at the data in red rectangle?

I will check the actual analog signal in detail on the scope tomorrow. My brains are done for today...

Paul

The 16 data bits are in the middle of the 32 Bit bit (8 msb and 8 lsb ignored..)

Or it works with (2x)24 bit frames , too. Have not tried that. Edit: The SAA7345 seems to use that.

Would be nice to know: Does the PT8211 work too with this format?

I remember the issue that (other than advertised) it does not output left and right in sync. Maybe it does, with this format?

Or it works with (2x)24 bit frames , too. Have not tried that. Edit: The SAA7345 seems to use that.

Would be nice to know: Does the PT8211 work too with this format?

I remember the issue that (other than advertised) it does not output left and right in sync. Maybe it does, with this format?

Last edited:

PaulS

Well-known member

Yeah, I guess the TDA1543A just assumes 24-bit right-justified 2's-complement data [some EIAJ format] and simply discards the first 8 bits [and whatever comes after the following 16 bits]

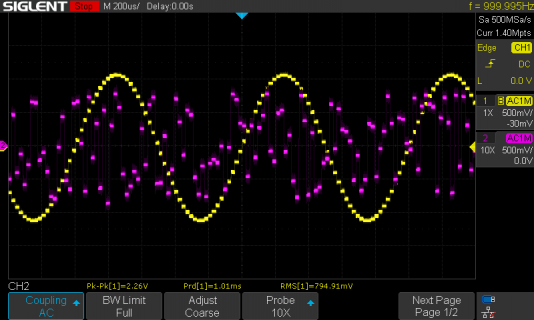

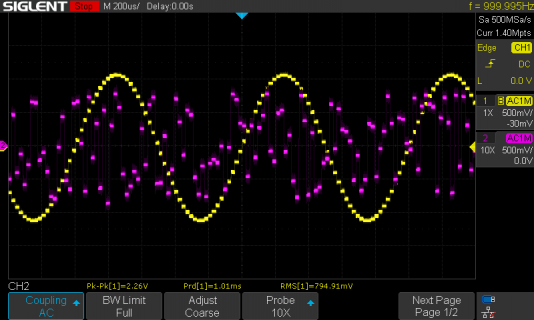

Yellow trace: TDA1543A, 1KHz, full scale output. Purple trace: PT2811.

Gruesse,

Paul

Unfortunately not:Would be nice to know: Does the PT8211 work too with this format?

Yellow trace: TDA1543A, 1KHz, full scale output. Purple trace: PT2811.

Gruesse,

Paul

- Status

- Not open for further replies.