ghostintranslation

Well-known member

Hi,

I'm usually using I2C devices, but this time I'm interested in the TLC5916 which is SPI:

https://www.ti.com/lit/ds/symlink/t...-digikeymode-dsf-pf-null-wwe&ts=1622292689320

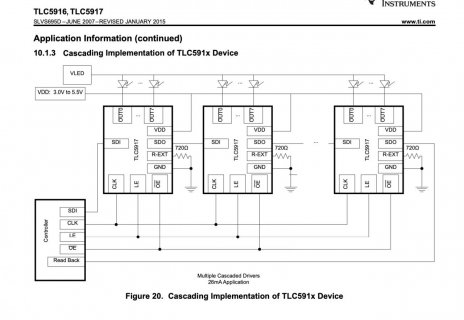

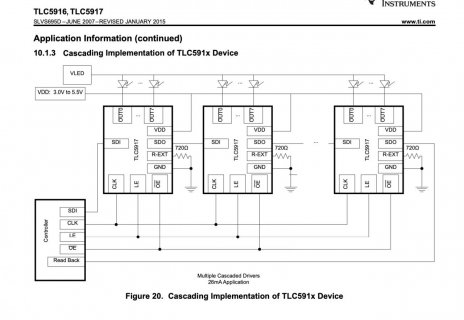

Usually from what I understand is that each SPI device has a select pin so that it set the device to listen to the bus. But in this documentation they also show a "cascade" implementation:

I see the SDO of the first device going in the SDI of the next device, but how does that work then? In this configuration can I still address each device separately or are they all going to be acting as just the same one device?

Thanks

I'm usually using I2C devices, but this time I'm interested in the TLC5916 which is SPI:

https://www.ti.com/lit/ds/symlink/t...-digikeymode-dsf-pf-null-wwe&ts=1622292689320

Usually from what I understand is that each SPI device has a select pin so that it set the device to listen to the bus. But in this documentation they also show a "cascade" implementation:

I see the SDO of the first device going in the SDI of the next device, but how does that work then? In this configuration can I still address each device separately or are they all going to be acting as just the same one device?

Thanks