Hi all,

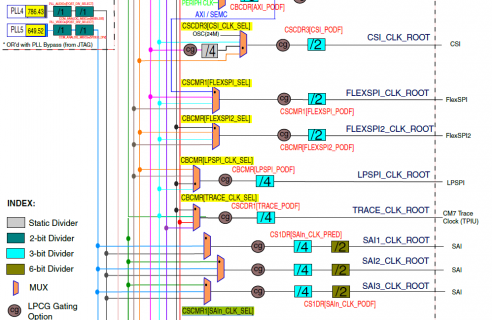

I read with great attention the vga code using flexio 1/2 and dma to have a functional 8 bit vga using teensy 4.1. I try to build a tft interface for a buffer less contrôler. I need pixel clock for that to go on an output pin. I looked/crawled in the super long reference manual and I could not identify how to get pll5 on an output pin. For sure pll5 can be fed to multiple blocks but I did not saw an output pin possibility so far… any help appreciated!

Thanks in advance

I read with great attention the vga code using flexio 1/2 and dma to have a functional 8 bit vga using teensy 4.1. I try to build a tft interface for a buffer less contrôler. I need pixel clock for that to go on an output pin. I looked/crawled in the super long reference manual and I could not identify how to get pll5 on an output pin. For sure pll5 can be fed to multiple blocks but I did not saw an output pin possibility so far… any help appreciated!

Thanks in advance