Hi there,

I'm trying to make work a Cirrus WM8782 based ADC board, which comes with its own clock. When plugged via secondary I2S_2 in Master mode it doesn't work, only a pattern noise comes out of the Teensy. In slave mode using the T4.1 MCLK and while the PJRC Audio Shield is plugged it works fine.

Strange enough the WM8782 is set to 44100Hz (11.2896M 256fs) and 16bit, which is what the Teensy seems to require.

Any idea what might be happening?

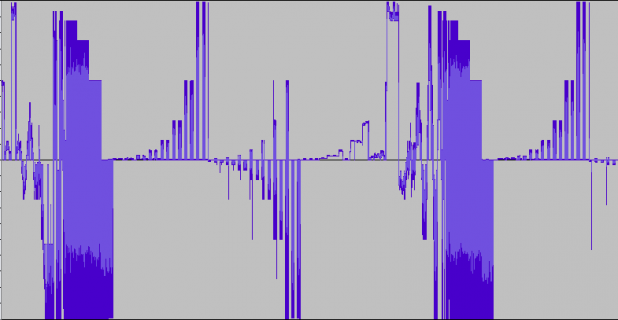

Please find a screenshot of the waveform I get. Only LRCLK, BCLK and DIN are connected.

Here a link of the datasheet and board used:

https://www.audiophonics.fr/en/devi...dc-board-wm8782-i2s-24bit-192khz-p-14897.html

https://statics.cirrus.com/pubs/proDatasheet/WM8782_v4.8.pdf

Thanks in advance,

Domingo

I'm trying to make work a Cirrus WM8782 based ADC board, which comes with its own clock. When plugged via secondary I2S_2 in Master mode it doesn't work, only a pattern noise comes out of the Teensy. In slave mode using the T4.1 MCLK and while the PJRC Audio Shield is plugged it works fine.

Strange enough the WM8782 is set to 44100Hz (11.2896M 256fs) and 16bit, which is what the Teensy seems to require.

Any idea what might be happening?

Please find a screenshot of the waveform I get. Only LRCLK, BCLK and DIN are connected.

Here a link of the datasheet and board used:

https://www.audiophonics.fr/en/devi...dc-board-wm8782-i2s-24bit-192khz-p-14897.html

https://statics.cirrus.com/pubs/proDatasheet/WM8782_v4.8.pdf

Thanks in advance,

Domingo