I am working on an SDR project where I need to sample and then synchronously process two IQ IF signals using WM8731 audio codecs. I have the codecs and RF parts working fine, but I have not yet found a way to reliably synchronize the two I2S buses and codecs so that my SDR code gets fed samples taken at exactly the same time from the two codecs. There seems to be an uncertain skew between the sampling of the two codecs from power cycle to power cycle.

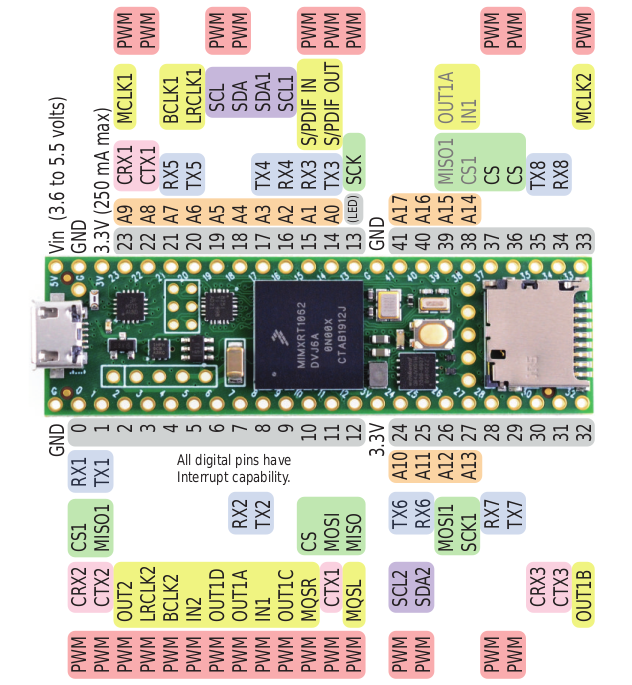

Is there a way of making sure that I2S1 and I2S2 of the Teensy 4 start operating at precisely the same clock cycle? I have read through the relevant parts of the processor data sheet, but not found any obvious solution. I tried the following, but it does not seem to resolve the issue:

And later:

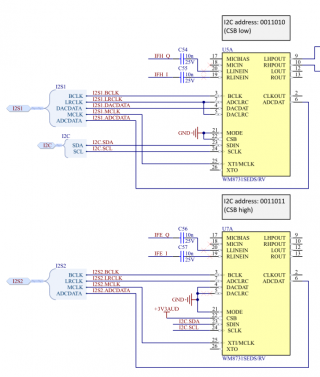

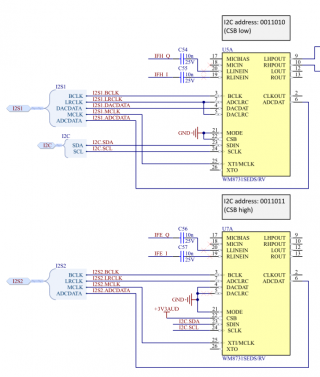

I currently run the two I2S interfaces of the Teensy 4 as masters and the WM8731s as slaves. Here is the part of the schematic showing the codecs:

Would it perhaps be easier to synchronize things if e.g. only I2S1 is master and route its clocks to both codecs while I2S2 would then operate as a slave? I do not have much experience with I2S, so I might be missing something obvious.

Is there a way of making sure that I2S1 and I2S2 of the Teensy 4 start operating at precisely the same clock cycle? I have read through the relevant parts of the processor data sheet, but not found any obvious solution. I tried the following, but it does not seem to resolve the issue:

Code:

AudioOutputI2S::config_i2s(false);

AudioOutputI2S2::config_i2s(false);

// Disable the DMA channels

AudioInputI2S::dma.disable();

AudioInputI2S2::dma.disable();

// Reset the I2S receivers

uint32_t I2S_RCSR_SR = 1<<24;

I2S1_RCSR = I2S_RCSR_FR | I2S_RCSR_SR; // page 2000, reset FIFO, software reset

I2S2_RCSR = I2S_RCSR_FR | I2S_RCSR_SR; // page 2000, reset FIFO, software resetAnd later:

Code:

// Enable I2S receivers

I2S1_RCSR = I2S_RCSR_RE | I2S_RCSR_BCE | I2S_RCSR_FRDE | I2S_RCSR_FR; // Enable, reset FIFO

I2S2_RCSR = I2S_RCSR_RE | I2S_RCSR_BCE | I2S_RCSR_FRDE | I2S_RCSR_FR; // Enable, reset FIFO

// Enable DMA

AudioInputI2S::dma.enable();

AudioInputI2S2::dma.enable();I currently run the two I2S interfaces of the Teensy 4 as masters and the WM8731s as slaves. Here is the part of the schematic showing the codecs:

Would it perhaps be easier to synchronize things if e.g. only I2S1 is master and route its clocks to both codecs while I2S2 would then operate as a slave? I do not have much experience with I2S, so I might be missing something obvious.