lilltroll77

Member

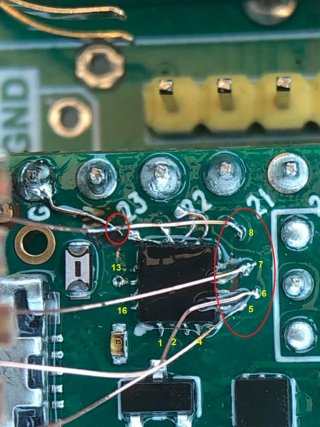

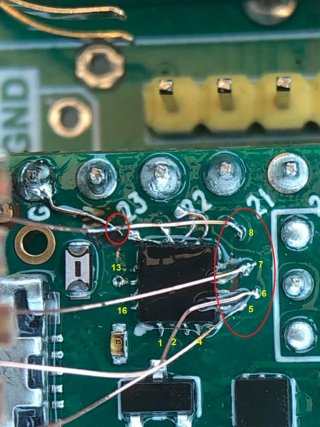

Below is my simple mod to add JTAG with UART to Teensy 4.1.

Tools needed:

Small screwdriver, small solder tip, small knife, optical magnification, Isopropanol and good flux.

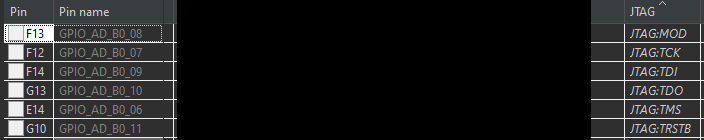

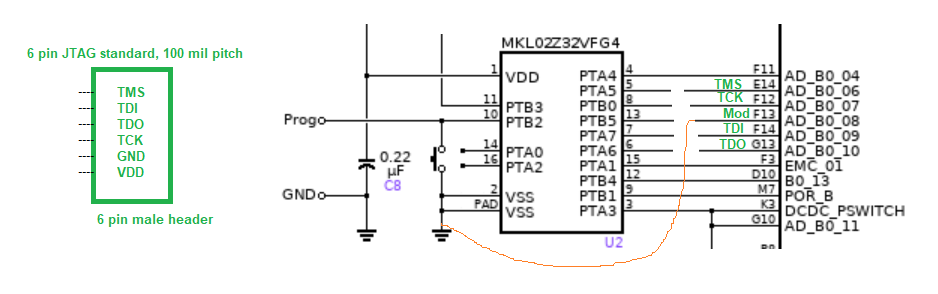

YOU ONLY NEED TO MOD PIN 5-8 and pin 13!

I have just played around with the Cortex M0 chip to understand how things work.

A RT1010-EVK flashed with Segger JTAG firmware.

The vias for pin 5-8 are easily accessible for the MKL02 chip.

Rub off the solder mask on the vias with a small screwdriver and Isopropanol. Flux the free copper, and add solder to (the top-side of) the vias. Make 2 parallel cuts with a sharp knife between the pads and the via. DO NOT CUT DEEP! Peel off the copper between the cuts for pin 5-8. Solder four thin wires to the four vias. You now have the JTAG connection. I made a JTAG-header above the USB connector.

If you want to use the NXP specific JTAG, you need to cut the copper from pin 13 - JTAG_MOD, and ground (on the RT1062 side) it to the G pin instead.

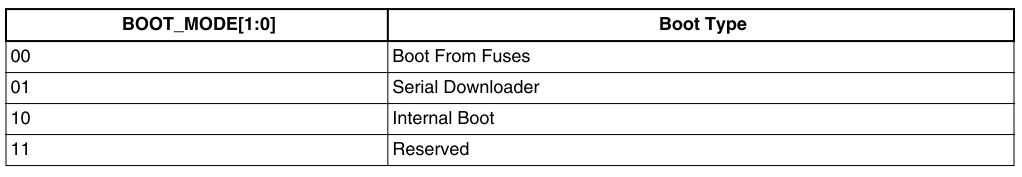

Teensy will still boot from Flash, if no JTAG is connected.

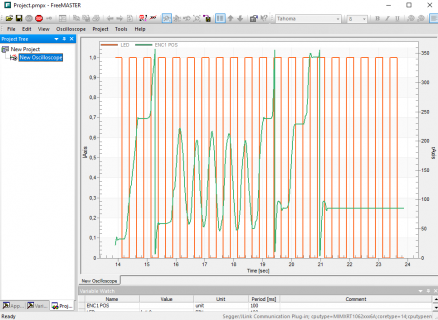

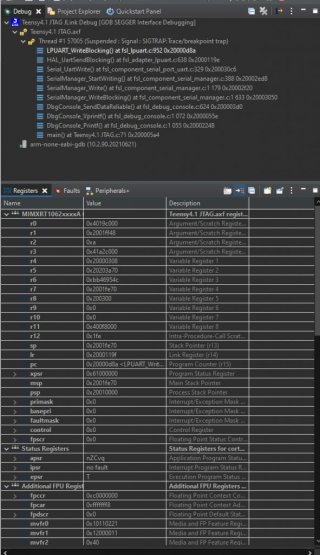

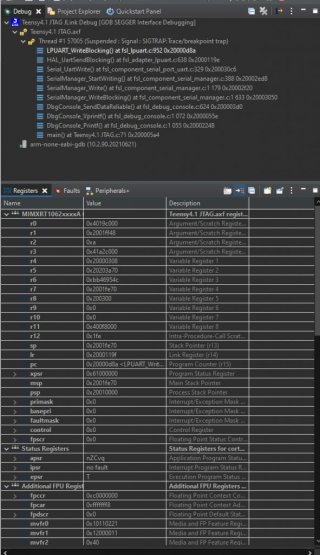

I my case, I have a custom board connected to Teensy, so I redirected PRINTF to UART7, and connected that pin to the UART pin of my "Segger" JTAG thing.

I can now debug my Teensy in MCUXpresso, and Hello world prints to the terminal in MCUXpresso.

If it's your first time doing HW hack like this, train on some other (broken) PCB first. Any old computer PCB, should be good for training.

Tools needed:

Small screwdriver, small solder tip, small knife, optical magnification, Isopropanol and good flux.

YOU ONLY NEED TO MOD PIN 5-8 and pin 13!

I have just played around with the Cortex M0 chip to understand how things work.

A RT1010-EVK flashed with Segger JTAG firmware.

The vias for pin 5-8 are easily accessible for the MKL02 chip.

Rub off the solder mask on the vias with a small screwdriver and Isopropanol. Flux the free copper, and add solder to (the top-side of) the vias. Make 2 parallel cuts with a sharp knife between the pads and the via. DO NOT CUT DEEP! Peel off the copper between the cuts for pin 5-8. Solder four thin wires to the four vias. You now have the JTAG connection. I made a JTAG-header above the USB connector.

If you want to use the NXP specific JTAG, you need to cut the copper from pin 13 - JTAG_MOD, and ground (on the RT1062 side) it to the G pin instead.

Teensy will still boot from Flash, if no JTAG is connected.

I my case, I have a custom board connected to Teensy, so I redirected PRINTF to UART7, and connected that pin to the UART pin of my "Segger" JTAG thing.

I can now debug my Teensy in MCUXpresso, and Hello world prints to the terminal in MCUXpresso.

If it's your first time doing HW hack like this, train on some other (broken) PCB first. Any old computer PCB, should be good for training.

Last edited: