I am occaisionally seeing extraneous interrupts occurring on a GPIO pin driven by a 250 Hz pulse train.

I am using Teesyduino 1.56 in PlatformIO on a T4.1.

I have set up the GPIO pin as an input with hysteresis and pulldown:

and this is my ISR:

microsCount() is actually using the 600Hz cycle counter to avoid any issue calling micros():

Occaisionally, maybe 3 times in 30 minutes for a 250 Hz pulse train, the ISR apparently triggers also on the falling edge in addition to the rising edge.

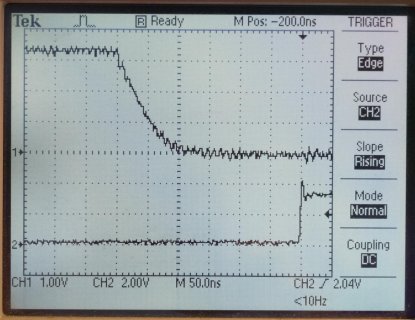

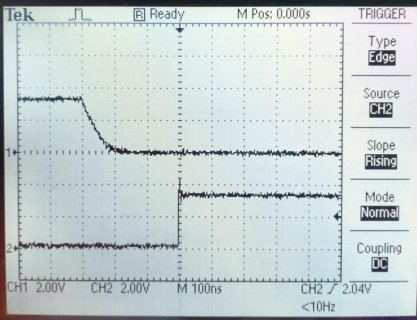

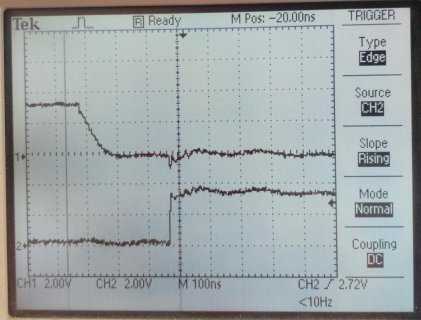

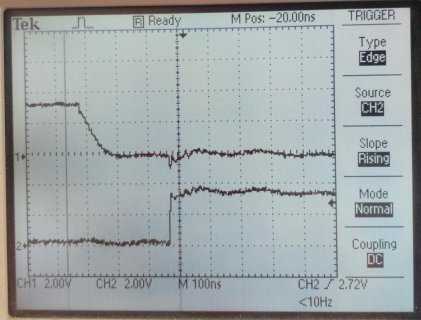

This is a scope capture of the unexpected behavior, where the DEBUG_GPIO_PIN0 goes high when the interrupt occurs sooner than expected. The scope is only 100MHz so it may be that I cannot see noise generating another rising edge trigger.

The slow transition time of 60 ns exceeds the datasheet stated minimum of 25 ns, and for that reason I added the hysteresis, but it did not affect the symptom.

Any help or comments would be very welcome.

Thanks!

I am using Teesyduino 1.56 in PlatformIO on a T4.1.

I have set up the GPIO pin as an input with hysteresis and pulldown:

Code:

pinMode(MAGDATA_PULSE_PIN, INPUT_PULLDOWN);

Code:

void magdataPulseISR( void ) {

static uint32_t lastTck =magdataPulseTimeUS;

static uint32_t diffTck = 0;

static bool firstTime = true;

DEBUG_GPIO_PIN0_CLEAR;

magdataPulseTimeUS = microsCount();

diffTck = magdataPulseTimeUS - lastTck;

if (!firstTime && (diffTck < 2000000)) { // trigger on frequency >> 250 Hz

DEBUG_GPIO_PIN0_SET;

capturedMagdataPulseTimeUS = magdataPulseTimeUS;

}

circular_buf_put(&magDataTimeUS_queue, magdataPulseTimeUS);

magdataPulseIntCount++;

firstTime = false;

lastTck = magdataPulseTimeUS;

asm volatile ("dsb");

}

Code:

uint32_t microsCount(void) {

return ARM_DWT_CYCCNT;

// WAS: return micros();

}This is a scope capture of the unexpected behavior, where the DEBUG_GPIO_PIN0 goes high when the interrupt occurs sooner than expected. The scope is only 100MHz so it may be that I cannot see noise generating another rising edge trigger.

The slow transition time of 60 ns exceeds the datasheet stated minimum of 25 ns, and for that reason I added the hysteresis, but it did not affect the symptom.

Any help or comments would be very welcome.

Thanks!