Hi all

I am working on a high speed logging type device with an external ADC connected by SPI to the T4.1.

There is a single ISR that is triggered by the ADC data ready line going low, this is connected to the T4.1 pin 28.

I am seeing a regular blowout of the ISR interval delta even though I have tried to set the priority very high with: NVIC_SET_PRIORITY(IRQ_GPIO1_16_31, 0);

Nb: Iam a little confused as to what IRQ group I should be using for pin 28. This seems to map into D5 and then EMC_32.

I am using teensythreads https://github.com/ftrias/TeensyThreads to allow for some low priority comman line interfacing etc to take place.

I suspect that my interrupts priorities are not being set as high as I had hoped, and the threads are simply interrupting....

I guess before I go any further, can someone advise if I have mapped the correct IO group in this IRQ priority setting?

Is there a document that explains the relationship between the pin labels in the teensy 4.1 schematic and the GPIO IRQ groups?

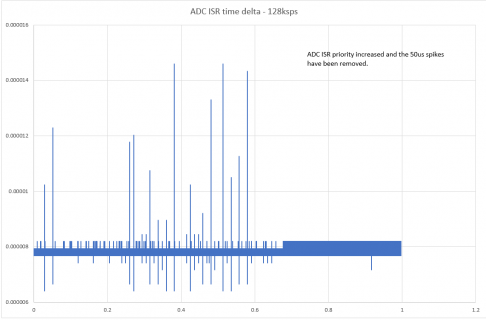

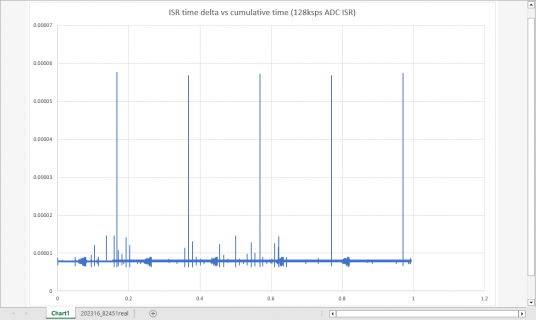

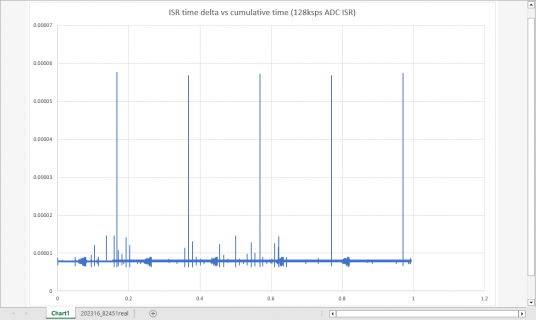

here is a plot of the phenomenon - chart shows the ISR time delta (between calls) vs cumulative time. Typical is 7.8us and when the issue occurs this streches out to up to 50us.

It is occuring at about at 200ms interval.

I am working on a high speed logging type device with an external ADC connected by SPI to the T4.1.

There is a single ISR that is triggered by the ADC data ready line going low, this is connected to the T4.1 pin 28.

I am seeing a regular blowout of the ISR interval delta even though I have tried to set the priority very high with: NVIC_SET_PRIORITY(IRQ_GPIO1_16_31, 0);

Nb: Iam a little confused as to what IRQ group I should be using for pin 28. This seems to map into D5 and then EMC_32.

I am using teensythreads https://github.com/ftrias/TeensyThreads to allow for some low priority comman line interfacing etc to take place.

I suspect that my interrupts priorities are not being set as high as I had hoped, and the threads are simply interrupting....

I guess before I go any further, can someone advise if I have mapped the correct IO group in this IRQ priority setting?

Is there a document that explains the relationship between the pin labels in the teensy 4.1 schematic and the GPIO IRQ groups?

here is a plot of the phenomenon - chart shows the ISR time delta (between calls) vs cumulative time. Typical is 7.8us and when the issue occurs this streches out to up to 50us.

It is occuring at about at 200ms interval.