@Rezo

Here is the FlexIO2 pin usage I am using:

FlexIO2------- Dev Board-------- ER-TFTM101-1 Pin

2:00 -----------> B0_00 -----------> /WR ---> 05

2:01 -----------> B0_01 -----------> /RD ---> 06

2:02 -----------> B0_02 ----------->

2:03 -----------> B0_03 ----------->

2:04 -----------> B0_04 -----------> D0 ----> 15

2:05 -----------> B0_05 -----------> D1 ----> 16

2:06 -----------> B0_06 -----------> D2 ----> 17

2:07 -----------> B0_07 -----------> D3 ----> 18

2:08 -----------> B0_08 -----------> D4 ----> 19

2:09 -----------> B0_09 -----------> D5 ----> 20

2:10 -----------> B0_10 -----------> D6 ----> 21

2:11 -----------> B0_11 -----------> D7 ----> 22

2:12 -----------> B0_12 -----------> D8 ----> 23

2:13 -----------> B0_13 -----------> D9 ----> 24

2:14 -----------> B0_14 -----------> D10 ----> 25

2:15 -----------> B0_15 -----------> D11 ----> 26

2:16 -----------> B1_00 -----------> D12 ----> 27

2:17 -----------> B1_01 -----------> D13 ----> 28

2:18 -----------> B1_02 -----------> D14 ----> 29

2:19 -----------> B1_03 -----------> D15 ----> 30

Finally have a stable and predictable setup on the T4.1. The maximum effective speeed is 20 MHz.

It is limited by the speed of the RA8876 2D engine. The only problem left with the T4.1 is 8-bit

memory reads. It still returns inconsistent values. 8/16 reads and write are good. 16-bit reads

are also good. It's just 8-bit reads that are not consistent.

An 8-bit read:

Code:

Teensy 4.1 and RA8876 parallel 8080 mode testing (8/16)

Bus speed: 2 MHZ

Bus Width: 8-bits

lcdDataread16(): Dummy 0x00ff, data 0x00ff

rslt = 0xFFFF <---------- incorrect value

Press anykey to continue

lcdDataread16(): Dummy 0x0001, data 0x00ff

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0x0001, data 0x00ff

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0x0001, data 0x0001

rslt = 0x0101 <---------- incorrect value

Press anykey to continue

A 16-bit read:

Code:

Teensy 4.1 and RA8876 parallel 8080 mode testing (8/16)

Bus speed: 2 MHZ

Bus Width: 16-bits

lcdDataread16(): Dummy 0x0100, data 0xff01

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0xff01, data 0xff01

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0xff01, data 0xff01

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0xff01, data 0xff01

rslt = 0x01FF <---------- correct value

Press anykey to continue

lcdDataread16(): Dummy 0xff01, data 0xff01

rslt = 0x01FF <---------- correct value

Press anykey to continue

Here are some speed tests using the 2D BTE (Block Transfer Engine) to write an image

to the display memory "lcd.writeRect(0,0,480,320,flexio_teensy_mm)":

Code:

Teensy 4.1 and RA8876 parallel 8080 mode testing (8/16 bits)

Bus speed: 12 MHz

Bus Width: 8-bits

Wrote 153600 bytes in 26ms

Bus speed: 12 MHz

Bus Width: 16-bits

Wrote 153600 bytes in 13ms

Bus speed: 20 MHz

Bus Width: 8-bits

Wrote 153600 bytes in 20ms

Bus speed: 20 MHz

Bus Width: 16-bits

Wrote 153600 bytes in 10ms

Bus speed: 24 MHz

Bus Width: 8-bits

Wrote 153600 bytes in 20ms

Bus speed: 24 MHz

Bus Width: 16-bits

Wrote 153600 bytes in 10ms

20MHz seems to be the max speed of the RA8876 2D engine and as expected 16-bits is twice as fast as 8-bits.

I can now use the working driver information as a control to compare with the SDRAM board.

Here is the T4.1 working initialization code:

Code:

#define BUS_WIDTH 8 /*Available options are 8 or 16 */

#define SHIFTER_DMA_REQUEST 3 // only 0, 1, 2, 3 expected to work

#define SHIFTNUM 8 // number of shifters used (up to 8)

#define BYTES_PER_BEAT (sizeof(uint8_t))

#define BEATS_PER_SHIFTER (sizeof(uint32_t)/BYTES_PER_BEAT)

#define BYTES_PER_BURST (sizeof(uint32_t)*SHIFTNUM)

#define SHIFTER_IRQ (SHIFTNUM-1)

#define TIMER_IRQ 0

#define FLEXIO_ISR_PRIORITY 64 // interrupt is timing sensitive, so use relatively high priority (supersedes USB)

FASTRUN void RA8876_t3::FlexIO_Init()

{

#if defined(USE_MM) // Or SDRAM board.

/* Get a FlexIO channel */

pFlex = FlexIOHandler::flexIOHandler_list[1]; // use FlexIO2

/* Pointer to the port structure in the FlexIO channel */

p = &pFlex->port();

/* Pointer to the hardware structure in the FlexIO channel */

hw = &pFlex->hardware();

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_00 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_01 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_04 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_05 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_06 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_07 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_08 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_09 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_10 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_11 = 4;

digitalWriteFast(10,HIGH);

digitalWriteFast(12,HIGH);

/* High speed and drive strength configuration */

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_00 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_01 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_04 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_05 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_06 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_07 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_08 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_09 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_10 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_11 = 0xFF;

if(BUS_WIDTH == 16) {

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_12 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_13 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_14 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B0_15 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_00 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_01 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_02 = 4;

IOMUXC_SW_MUX_CTL_PAD_GPIO_B1_03 = 4;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_12 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_13 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_14 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B0_15 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_00 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_01 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_02 = 0xFF;

IOMUXC_SW_PAD_CTL_PAD_GPIO_B1_03 = 0xFF;

}

/* Set clock */

pFlex->setClockSettings(3, 1, 0); // (480 MHz source, 1+1, 1+0) >> 480/2/1 >> 240Mhz

/* Enable the clock */

hw->clock_gate_register |= hw->clock_gate_mask ;

/* Enable the FlexIO with fast access */

p->CTRL = FLEXIO_CTRL_FLEXEN;// | FLEXIO_CTRL_FASTACC;

#else // T4.1 setup

/* Get a FlexIO channel */

pFlex = FlexIOHandler::flexIOHandler_list[2]; // use FlexIO3

/* Pointer to the port structure in the FlexIO channel */

p = &pFlex->port();

/* Pointer to the hardware structure in the FlexIO channel */

hw = &pFlex->hardware();

/* Basic pin setup */

pinMode(19, OUTPUT); // FlexIO3:0 D0

pinMode(18, OUTPUT); // FlexIO3:1 |

pinMode(14, OUTPUT); // FlexIO3:2 |

pinMode(15, OUTPUT); // FlexIO3:3 |

pinMode(40, OUTPUT); // FlexIO3:4 |

pinMode(41, OUTPUT); // FlexIO3:5 |

pinMode(17, OUTPUT); // FlexIO3:6 |

pinMode(16, OUTPUT); // FlexIO3:7 D7

#if (BUS_WIDTH == 16)

pinMode(22, OUTPUT); // FlexIO3:8 D8

pinMode(23, OUTPUT); // FlexIO3:9 |

pinMode(20, OUTPUT); // FlexIO3:10 |

pinMode(21, OUTPUT); // FlexIO3:11 |

pinMode(38, OUTPUT); // FlexIO3:12 |

pinMode(39, OUTPUT); // FlexIO3:13 |

pinMode(26, OUTPUT); // FlexIO3:14 |

pinMode(27, OUTPUT); // FlexIO3:15 D15

#endif

pinMode(36, OUTPUT);

digitalWriteFast(36, HIGH);

pinMode(37, OUTPUT);

digitalWriteFast(37, HIGH);

/* High speed and drive strength configuration */

*(portControlRegister(36)) = 0xFF;

*(portControlRegister(37)) = 0xFF;

*(portControlRegister(19)) = 0xFF;

*(portControlRegister(18)) = 0xFF;

*(portControlRegister(14)) = 0xFF;

*(portControlRegister(15)) = 0xFF;

*(portControlRegister(40)) = 0xFF;

*(portControlRegister(41)) = 0xFF;

*(portControlRegister(17)) = 0xFF;

*(portControlRegister(16)) = 0xFF;

#if (BUS_WIDTH == 16)

*(portControlRegister(22)) = 0xFF;

*(portControlRegister(23)) = 0xFF;

*(portControlRegister(20)) = 0xFF;

*(portControlRegister(21)) = 0xFF;

*(portControlRegister(38)) = 0xFF;

*(portControlRegister(39)) = 0xFF;

*(portControlRegister(26)) = 0xFF;

*(portControlRegister(27)) = 0xFF;

#endif

/* Set clock */

pFlex->setClockSettings(3, 1, 0); // (480 MHz source, 1+1, 1+0) >> 480/2/1 >> 240Mhz

/* Set up pin mux */

pFlex->setIOPinToFlexMode(36);

pFlex->setIOPinToFlexMode(37);

pFlex->setIOPinToFlexMode(19);

pFlex->setIOPinToFlexMode(18);

pFlex->setIOPinToFlexMode(14);

pFlex->setIOPinToFlexMode(15);

pFlex->setIOPinToFlexMode(40);

pFlex->setIOPinToFlexMode(41);

pFlex->setIOPinToFlexMode(17);

pFlex->setIOPinToFlexMode(16);

#if (BUS_WIDTH == 16)

pFlex->setIOPinToFlexMode(22);

pFlex->setIOPinToFlexMode(23);

pFlex->setIOPinToFlexMode(20);

pFlex->setIOPinToFlexMode(21);

pFlex->setIOPinToFlexMode(38);

pFlex->setIOPinToFlexMode(39);

pFlex->setIOPinToFlexMode(26);

pFlex->setIOPinToFlexMode(27);

#endif

hw->clock_gate_register |= hw->clock_gate_mask ;

/* Enable the FlexIO with fast access */

p->CTRL = FLEXIO_CTRL_FLEXEN;

#endif

}

The single beat read init:

Code:

FASTRUN void RA8876_t3::FlexIO_Config_SnglBeat_Read() {

#if defined(USE_MM) // Or SDRAM board

p->CTRL &= ~FLEXIO_CTRL_FLEXEN;

p->CTRL |= FLEXIO_CTRL_SWRST;

p->CTRL &= ~FLEXIO_CTRL_SWRST;

pFlex->setIOPinToFlexMode(12);

/* Configure the shifters */

p->SHIFTCFG[3] =

//FLEXIO_SHIFTCFG_INSRC /* Shifter input */

FLEXIO_SHIFTCFG_SSTOP(0) /* Shifter stop bit disabled */

| FLEXIO_SHIFTCFG_SSTART(0) /* Shifter start bit disabled and loading data on enabled */

| FLEXIO_SHIFTCFG_PWIDTH(BUS_WIDTH - 1); /* Bus width */

p->SHIFTCTL[3] =

FLEXIO_SHIFTCTL_TIMSEL(0) /* Shifter's assigned timer index */

| FLEXIO_SHIFTCTL_TIMPOL*(1) /* Shift on posedge of shift clock */

| FLEXIO_SHIFTCTL_PINCFG(0) /* Shifter's pin configured as input */

| FLEXIO_SHIFTCTL_PINSEL(4) //4 /* Shifter's pin start index */

| FLEXIO_SHIFTCTL_PINPOL*(0) //0 /* Shifter's pin active high */

| FLEXIO_SHIFTCTL_SMOD(1); /* Shifter mode as recieve */

/* Configure the timer for shift clock */

p->TIMCMP[0] =

(((1 * 2) - 1) << 8) /* TIMCMP[15:8] = number of beats x 2 – 1 */

| (((_baud_div)/2) - 1); //30 /* TIMCMP[7:0] = baud rate divider / 2 – 1 ::: 30 = 8Mhz with current controller speed */

p->TIMCFG[0] =

FLEXIO_TIMCFG_TIMOUT(0) /* Timer output logic one when enabled and not affected by reset */

| FLEXIO_TIMCFG_TIMDEC(0) /* Timer decrement on FlexIO clock, shift clock equals timer output */

| FLEXIO_TIMCFG_TIMRST(0) /* Timer never reset */

| FLEXIO_TIMCFG_TIMDIS(2) /* Timer disabled on timer compare */

| FLEXIO_TIMCFG_TIMENA(2) /* Timer enabled on trigger high */

| FLEXIO_TIMCFG_TSTOP(1) /* Timer stop bit disabled */

| FLEXIO_TIMCFG_TSTART*(0); /* Timer start bit disabled */

p->TIMCTL[0] =

FLEXIO_TIMCTL_TRGSEL((((3) << 2) | 1)) /* Timer trigger selected as shifter's status flag */

| FLEXIO_TIMCTL_TRGPOL*(1) /* Timer trigger polarity as active low */

| FLEXIO_TIMCTL_TRGSRC*(1) /* Timer trigger source as internal */

| FLEXIO_TIMCTL_PINCFG(3) /* Timer' pin configured as output */

| FLEXIO_TIMCTL_PINSEL(1) /* Timer' pin index: RD pin */

| FLEXIO_TIMCTL_PINPOL*(1) /* Timer' pin active low */

| FLEXIO_TIMCTL_TIMOD(1); /* Timer mode as dual 8-bit counters baud/bit */

/* Enable FlexIO */

p->CTRL |= FLEXIO_CTRL_FLEXEN;

#else

p->CTRL &= ~FLEXIO_CTRL_FLEXEN;

p->CTRL |= FLEXIO_CTRL_SWRST;

p->CTRL &= ~FLEXIO_CTRL_SWRST;

/* Configure the shifters */

p->SHIFTCFG[3] =

FLEXIO_SHIFTCFG_SSTOP(0) /* Shifter stop bit disabled */

| FLEXIO_SHIFTCFG_SSTART(0) /* Shifter start bit disabled and loading data on enabled */

| FLEXIO_SHIFTCFG_PWIDTH(BUS_WIDTH-1); /* Bus width */

p->SHIFTCTL[3] =

FLEXIO_SHIFTCTL_TIMSEL(0) /* Shifter's assigned timer index */

| FLEXIO_SHIFTCTL_TIMPOL*(1) /* Shift on negative edge of shift clock */

| FLEXIO_SHIFTCTL_PINCFG(1) /* Shifter's pin configured as output */

| FLEXIO_SHIFTCTL_PINSEL(0) /* Shifter's pin start index */

| FLEXIO_SHIFTCTL_PINPOL*(0) /* Shifter's pin active high */

| FLEXIO_SHIFTCTL_SMOD(1); /* Shifter mode as receive */

/* Configure the timer for shift clock */

p->TIMCMP[0] =

(((1 * 2) - 1) << 8) /* TIMCMP[15:8] = number of beats x 2 – 1 */

| ((60/2) - 1); /* TIMCMP[7:0] = baud rate divider / 2 – 1 */

p->TIMCFG[0] =

FLEXIO_TIMCFG_TIMOUT(0) /* Timer output logic one when enabled and not affected by reset */

| FLEXIO_TIMCFG_TIMDEC(0) /* Timer decrement on FlexIO clock, shift clock equals timer output */

| FLEXIO_TIMCFG_TIMRST(0) /* Timer never reset */

| FLEXIO_TIMCFG_TIMDIS(2) /* Timer disabled on timer compare */

| FLEXIO_TIMCFG_TIMENA(2) /* Timer enabled on trigger high */

| FLEXIO_TIMCFG_TSTOP(1) /* Timer stop bit enabled */

| FLEXIO_TIMCFG_TSTART*(0); /* Timer start bit disabled */

p->TIMCTL[0] =

FLEXIO_TIMCTL_TRGSEL((((3) << 2) | 1)) /* Timer trigger selected as shifter's status flag */

| FLEXIO_TIMCTL_TRGPOL*(1) /* Timer trigger polarity as active low */

| FLEXIO_TIMCTL_TRGSRC*(1) /* Timer trigger source as internal */

| FLEXIO_TIMCTL_PINCFG(3) /* Timer' pin configured as output */

| FLEXIO_TIMCTL_PINSEL(19) /* Timer' pin index: RD pin */

| FLEXIO_TIMCTL_PINPOL*(1) /* Timer' pin active low */

| FLEXIO_TIMCTL_TIMOD(1); /* Timer mode as dual 8-bit counters baud/bit */

pFlex->setIOPinToFlexMode(37);

/* Enable FlexIO */

p->CTRL |= FLEXIO_CTRL_FLEXEN;

#endif

}

These are the main low level access functions:

Code:

//**************************************************************//

// Read RA8876 status register 8bit data R/W only. 8/16 bit bus.

// Special case for status register access:

// /CS = 0, /DC = 0, /RD = 0, /WR = 1.

//**************************************************************//

ru8 RA8876_t3::lcdStatusRead(bool finalize)

{

while(WR_DMATransferDone == false) {} //Wait for any DMA transfers to complete

FlexIO_Config_SnglBeat_Read();

CSLow();

DCLow();

uint16_t data = 0;

while (0 == (p->SHIFTSTAT & (1 << 3))) {}

data = p->SHIFTBUFBYS[3];

DCHigh();

CSHigh();

//Serial.printf("Dummy 0x%4.4x, data 0x%4.4x\n", dummy, data);

//Set FlexIO back to Write mode

FlexIO_Config_SnglBeat();

if(BUS_WIDTH == 8)

return data;

else

return (data >> 8) & 0xff;

}

//**************************************************************//

// Read RA8876 parallel Data (8-bit read) 8/16 bit bus mode.

//**************************************************************//

ru8 RA8876_t3::lcdDataRead(bool finalize) {

uint16_t dummy = 0;

uint16_t data = 0;

while(WR_DMATransferDone == false) {} //Wait for any DMA transfers to complete

CSLow(); // Must to go low after config and delay above.

DCHigh(); // Should already be HIGH

FlexIO_Config_SnglBeat_Read();

while (0 == (p->SHIFTSTAT & (1 << 3))) {}

dummy = p->SHIFTBUFBYS[3];

while (0 == (p->SHIFTSTAT & (1 << 3))) {}

data = p->SHIFTBUFBYS[3];

// while(digitalReadFast(33) == 0); // If monitoring XnWAIT signal from RA8876.

CSHigh();

// Serial.printf("lcdDataread(): Dummy 0x%2.2x, data 0x%2.2x\n", dummy, data);

//Set FlexIO back to Write mode

FlexIO_Config_SnglBeat(); // Not sure if this is needed.

if(BUS_WIDTH == 8)

return data;

else

return (data >> 8) & 0xff;

}

//**************************************************************//

// 16 bit read RA8876 Data. 8/16 bit bus mode.

//**************************************************************//

uint16_t RA8876_t3::lcdDataRead16(bool finalize)

{

uint16_t dummy = 0;

uint16_t data = 0;

while(WR_DMATransferDone == false) {} //Wait for any DMA transfers to complete

CSLow(); // Must to go low after config and delay above.

DCHigh(); // Should already be HIGH

FlexIO_Config_SnglBeat_Read();

while (0 == (p->SHIFTSTAT & (1 << 3))) {}

dummy = p->SHIFTBUFBYS[3];

while (0 == (p->SHIFTSTAT & (1 << 3))) {}

data = p->SHIFTBUFBYS[3];

CSHigh();

// Serial.printf("lcdDataread16(): Dummy 0x%4.4x, data 0x%4.4x\n", dummy, data);

//Set FlexIO back to Write mode

FlexIO_Config_SnglBeat(); // Not sure if this is needed.

if(BUS_WIDTH == 8)

return (dummy << 8) | (data & 0xff); // High byte to low byte and mask.

else

return (data >> 8) | (data << 8);

}

//****************************************************************

// Write to a RA8876 register (8 bit only) in 8/16 bbit buss mode.

//****************************************************************

void RA8876_t3::lcdRegWrite(ru8 reg, bool finalize)

{

while(WR_IRQTransferDone == false) {} //Wait for any DMA transfers to complete

FlexIO_Config_SnglBeat();

CSLow();

DCLow();

/* Write command index */

p->SHIFTBUF[0] = reg;

/*Wait for transfer to be completed */

while(0 == (p->SHIFTSTAT & (1 << 0))) {}

while(0 == (p->TIMSTAT & (1 << 0))) {}

/* De-assert RS pin */

DCHigh();

CSHigh();

}

//*****************************************************************

// Write RA8876 Data 8 bit data reg or memory in 8/16 bit bus mode.

//*****************************************************************

void RA8876_t3::lcdDataWrite(ru8 data, bool finalize) {

while(WR_DMATransferDone == false) {}

FlexIO_Config_SnglBeat();

CSLow();

DCHigh();

p->SHIFTBUF[0] = data;

/*Wait for transfer to be completed */

while(0 == (p->SHIFTSTAT & (1 << 0))) {}

while(0 == (p->TIMSTAT & (1 << 0))) {}

// while(digitalReadFast(33) == 0); // If monitoring XnWAIT signal from RA8876.

CSHigh();

}

//*********************************************************

// Write RA8876 data to display memory, 8/16 bit buss mode.

//*********************************************************

void RA8876_t3::lcdDataWrite16(uint16_t data, bool finalize)

{

while(WR_DMATransferDone == false) {} //Wait for any DMA transfers to complete

FlexIO_Config_SnglBeat();

CSLow();

DCHigh();

if(BUS_WIDTH == 16) {

p->SHIFTBUF[0] = data;

while(0 == (p->SHIFTSTAT & (1 << 0))) {}

while(0 == (p->TIMSTAT & (1 << 0))) {}

} else {

p->SHIFTBUF[0] = data >> 8;

while(0 == (p->SHIFTSTAT & (1 << 0))) {}

p->SHIFTBUF[0] = data & 0xff;

while(0 == (p->SHIFTSTAT & (1 << 0))) {}

while(0 == (p->TIMSTAT & (1 << 0))) {}

}

//while(digitalReadFast(33) == 0); // If monitoring XnWAIT signal from RA8876.

/* De-assert /CS pin */

CSHigh();

}

Combinations of these functions are also used in other functions.

Now that I have a fairly stable library working on the T4.1 I will switch to the SDRAM board

and continue testing. 16-bit DMA is not working correctly yet, but that's next after getting

the basic communications working on the SDRAM board. The only other concern is if the trace

length of the SDRAM board with the three inch connecting wires are having an effect on the

SDRAM board. The traces are much shorter on the T4.1.

I really appreciate your help and advice. Sorry about the long post

I will let you know the results after I setup the SDRAM board again...

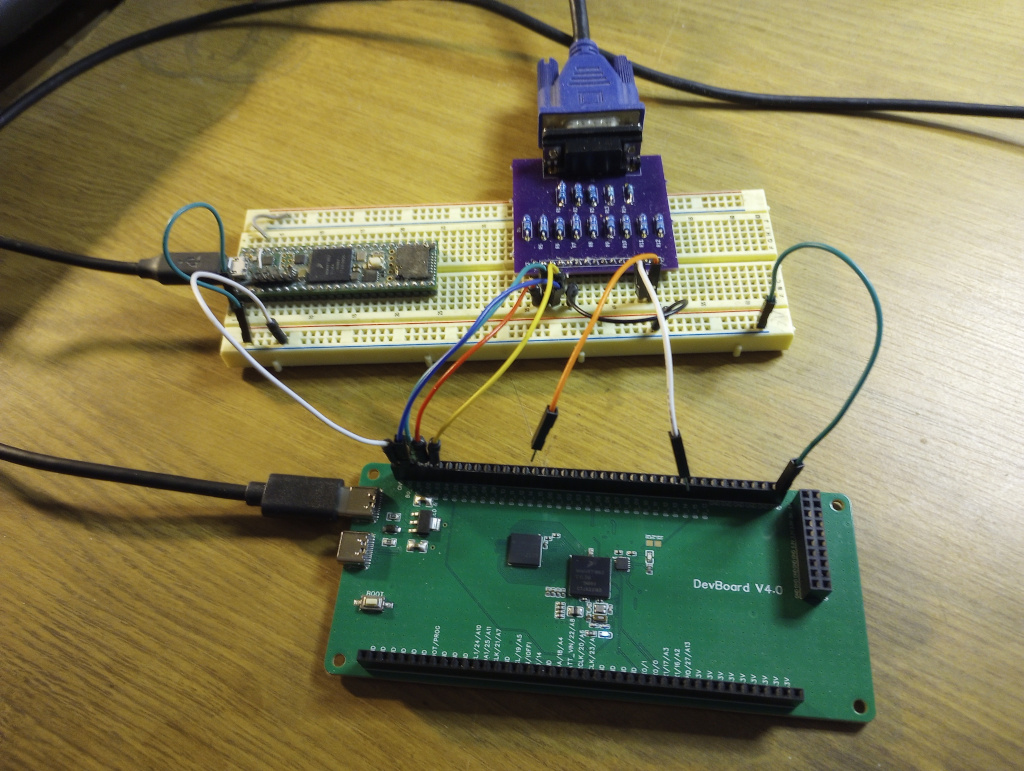

I ran through all of the test programs that I know about without a problem. I need to make sure I have all of the pinout info for this board. It is a version 4 board.

I ran through all of the test programs that I know about without a problem. I need to make sure I have all of the pinout info for this board. It is a version 4 board.