I am trying to implement a state machine in an isr, and find some interesting timing problems.

Here is a synopsis of how it works, but you can skip this for the question.

The external parts are an S11639-01 (CCD sensor) interfaced and a MCP33131D (ADC) which connects to the T4 by SPI. There is an output TRG from the CCD that is intended to serve as the convert trigger for an ADC. TRG runs continuously with a small offset from the master clock. Exposure begins when the T4 sets the ST pin high, and ends 48 clocks after setting ST low. At 88 clocks after ST goes low, the "video" signal is clocked to the output output pin. The ADC should start sampling then.

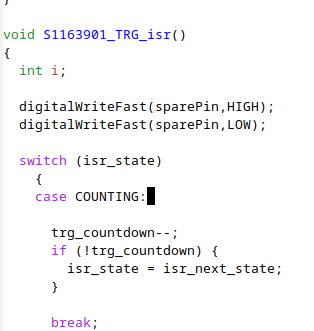

The following code snippet is from the top of the ISR, it simply sets a pin on entry to the ISR. "sparePin" is pin 2 on the T4.

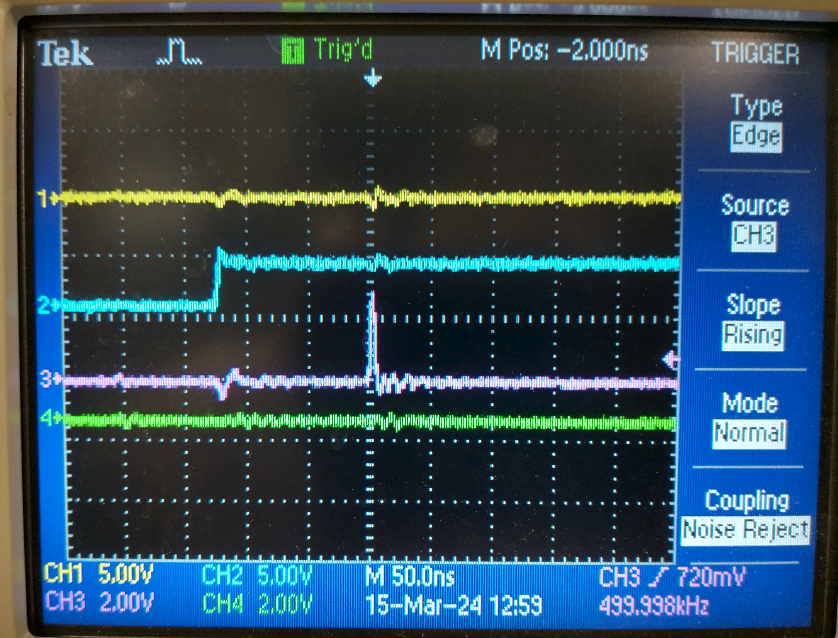

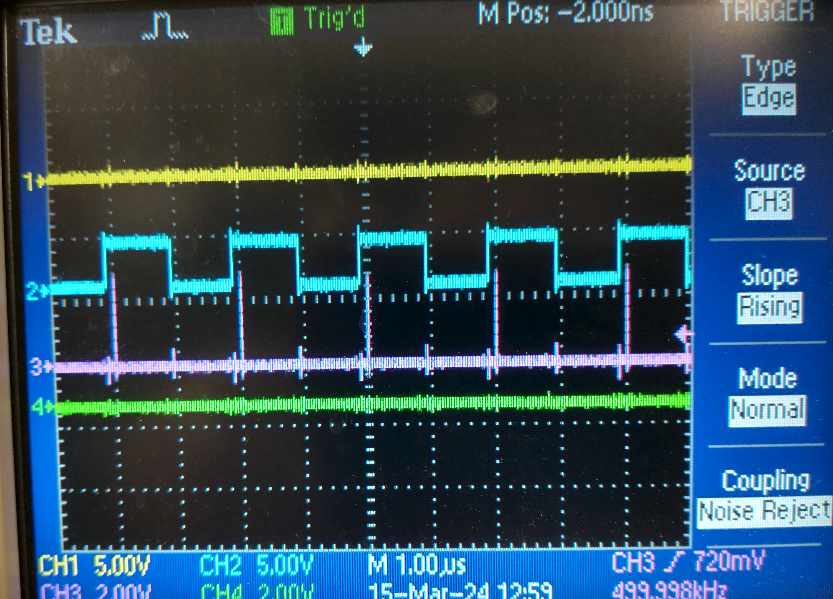

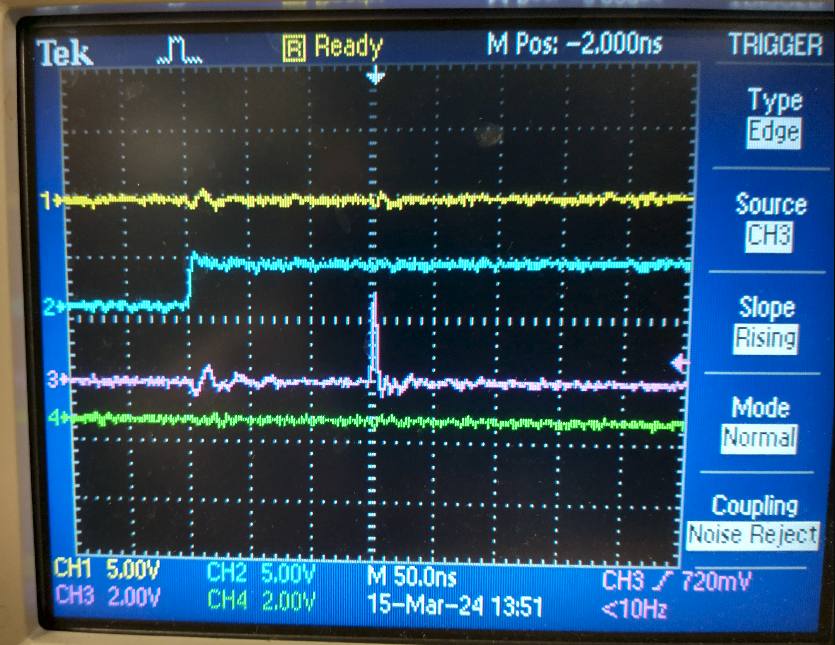

Here is a scope trace of what that looks like. The blue trace is the TRG signal, connect to pin 7 on the T4. The isr is attached to pin 7, rising edge. Notice the 120 nsec delay from the trigger until the pin is asserted in the ISR. The second image shows that the timing is constant.

So, that is a little surprising, it seems like it takes 72 instructions cycles to get to the ISR? On a bare metal platform, one would expect just a few instruction cycles to get to the isr, certainly under 10. Is there a away to speed this up?

Okay next issue.

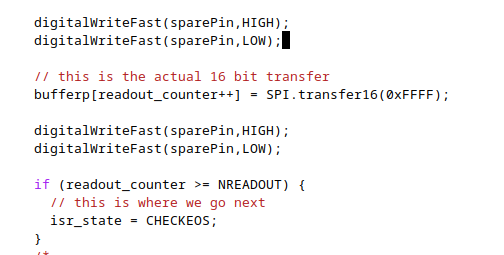

Here we are looking at the time to get to one of the switch statements. Here is the code snippet, followed by the scope trace. The time to get to the case, is now 150 nsecs, the extra 25 nsecs corresponds to about 15 instructions, that's okay, not a big deal. So that is not a problem.

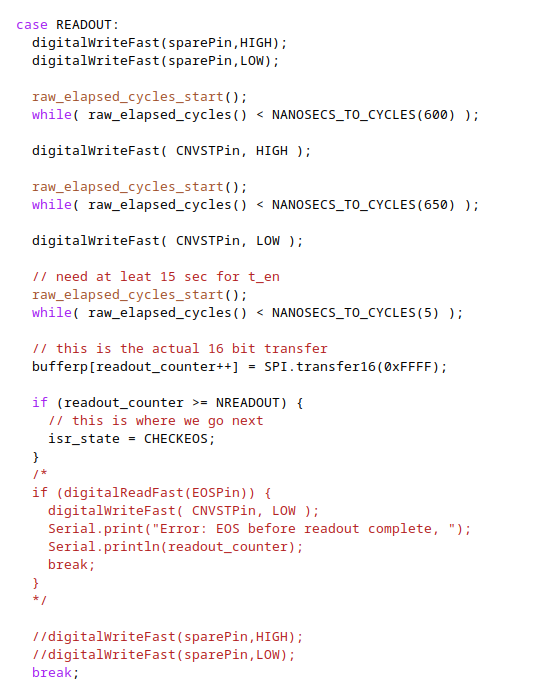

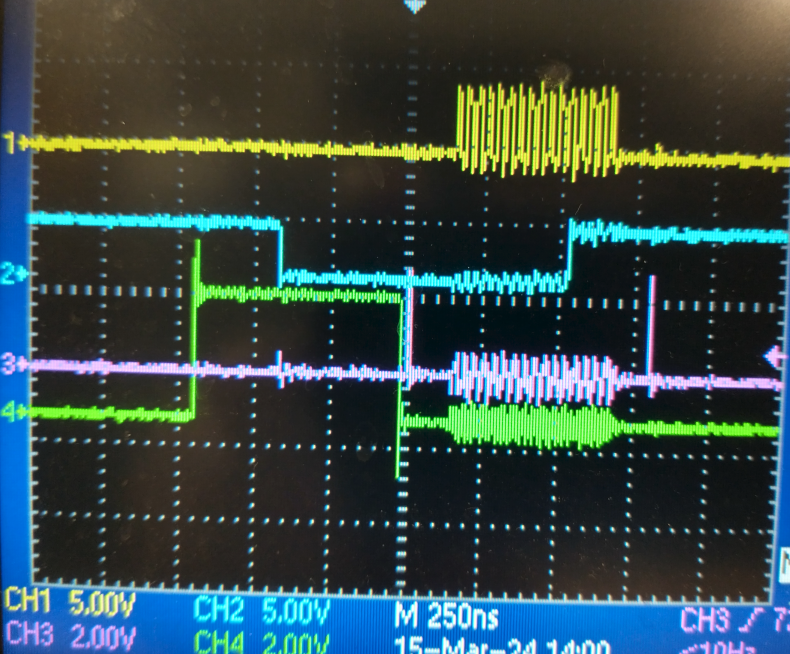

And finally, here is the ADC readout. First the code and then the traces. Notice there is about 150 nsecs before the transfer begins and another 100 nsecs afterwards. That extra 250 nsecs, is serious limitation for a readout 16 bits that should only take 533 nsecs at 30MHz. So, is there anyway to speed that up? I can move the 150nsecs inside the "convert" time so that the transfer actually starts promptly, but it would still be helpful to reduce the 100nsecs after.

Thank you

Here is a synopsis of how it works, but you can skip this for the question.

The external parts are an S11639-01 (CCD sensor) interfaced and a MCP33131D (ADC) which connects to the T4 by SPI. There is an output TRG from the CCD that is intended to serve as the convert trigger for an ADC. TRG runs continuously with a small offset from the master clock. Exposure begins when the T4 sets the ST pin high, and ends 48 clocks after setting ST low. At 88 clocks after ST goes low, the "video" signal is clocked to the output output pin. The ADC should start sampling then.

The following code snippet is from the top of the ISR, it simply sets a pin on entry to the ISR. "sparePin" is pin 2 on the T4.

Here is a scope trace of what that looks like. The blue trace is the TRG signal, connect to pin 7 on the T4. The isr is attached to pin 7, rising edge. Notice the 120 nsec delay from the trigger until the pin is asserted in the ISR. The second image shows that the timing is constant.

So, that is a little surprising, it seems like it takes 72 instructions cycles to get to the ISR? On a bare metal platform, one would expect just a few instruction cycles to get to the isr, certainly under 10. Is there a away to speed this up?

Okay next issue.

Here we are looking at the time to get to one of the switch statements. Here is the code snippet, followed by the scope trace. The time to get to the case, is now 150 nsecs, the extra 25 nsecs corresponds to about 15 instructions, that's okay, not a big deal. So that is not a problem.

And finally, here is the ADC readout. First the code and then the traces. Notice there is about 150 nsecs before the transfer begins and another 100 nsecs afterwards. That extra 250 nsecs, is serious limitation for a readout 16 bits that should only take 533 nsecs at 30MHz. So, is there anyway to speed that up? I can move the 150nsecs inside the "convert" time so that the transfer actually starts promptly, but it would still be helpful to reduce the 100nsecs after.

Thank you