You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Reading Eight Simultaneous Data Streams

- Thread starter matt7461

- Start date

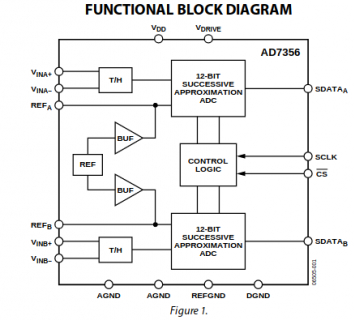

I think what I am really asking is if the Teensy is capable of reading from two SPI buses simultaneously. I have little experience with microcontrollers so I apologize if I am missing something obvious. I have attached the ADC's block diagram for reference.

Attachments

joepasquariello

Well-known member

MarkT is just saying it's not two buses. It's one bus, with one clock signal, and two receive data lines rather than out TX and one RX. See chapter 48 of the processor reference manual for the LPSPI peripheral, which contains the list of modes shown below. As far as I know, the Teensy SPI library only supports 1-bit transmit and/or receive on each clock, so if you wanted to do 2-bit receive on each clock, you'd have to tackle that. There is likely someone on the forum who has done it.

• Full duplex transfers supporting 1-bit transmit and receive on each clock edge

• Half duplex transfers supporting 1-bit transmit or receive on each clock edge

• Half duplex transfers supporting 2-bit transmit or receive on each clock edge (master only)

• Half duplex transfers supporting 4-bit transmit or receive on each clock edge (master only)

• Full duplex transfers supporting 1-bit transmit and receive on each clock edge

• Half duplex transfers supporting 1-bit transmit or receive on each clock edge

• Half duplex transfers supporting 2-bit transmit or receive on each clock edge (master only)

• Half duplex transfers supporting 4-bit transmit or receive on each clock edge (master only)