The PCB I designed seems to work ok when I do not connect a 1 foot connector of ribbon cable that breaks out the SPI lines as well as some other signals. When testing with the cable, the SPI seems to fail in having good communication with the 5 chips on the PCB, the cable is unconnected to anything but the PCB at this point. It does not look like I can connect more spi devices on the cable.

I am running the SPI at 1 MHz. I decided to take a look at the SPI clock to see what it might look like before and after the cable is attached. I figured at 1Mhz, it should not be a problem.

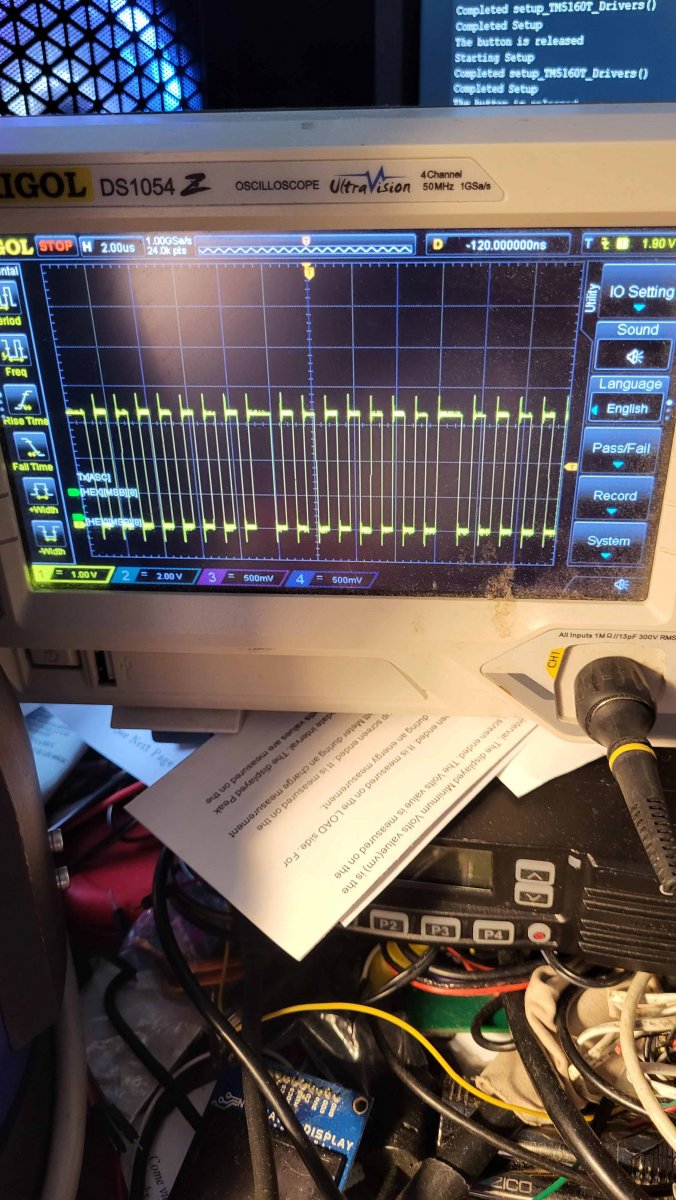

When my program is running and I scoped Pin 13, I see the below.....

Why are there 2 different frequencies on the SCK signal? It looks like a pattern at about 1Mhz and 100 Khz. I think I see this same pattern when the cable is either attached or not. In any case, what will this cause behavior? I would think that the SPI clock line should be a constant pattern/frequency if it is on and it could only be either on or off. For starters, to me this does not look proper..please advise

I am running the SPI at 1 MHz. I decided to take a look at the SPI clock to see what it might look like before and after the cable is attached. I figured at 1Mhz, it should not be a problem.

When my program is running and I scoped Pin 13, I see the below.....

Why are there 2 different frequencies on the SCK signal? It looks like a pattern at about 1Mhz and 100 Khz. I think I see this same pattern when the cable is either attached or not. In any case, what will this cause behavior? I would think that the SPI clock line should be a constant pattern/frequency if it is on and it could only be either on or off. For starters, to me this does not look proper..please advise