alexandros

Well-known member

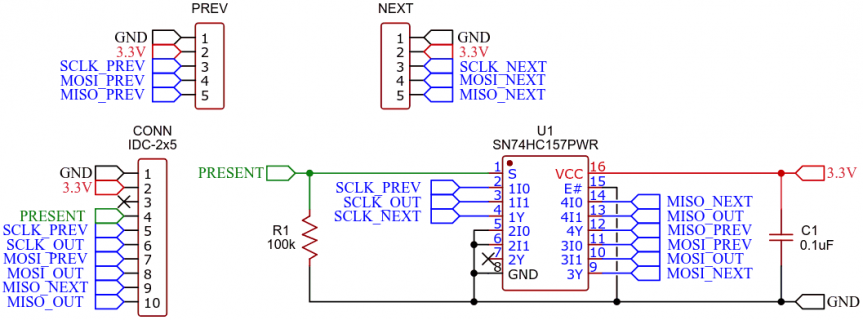

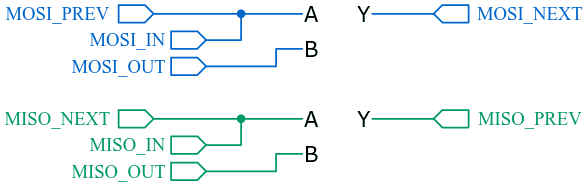

I'm trying to build a modular system where modules that contain shift registers can connect to a bus board. To avoid hard-coding the number and positions of these modules on the bus board (there are sixteen sockets where modules can connect, through IDC connectors), I'm trying to detect them, and route the MISO and MOSI signals accordingly.

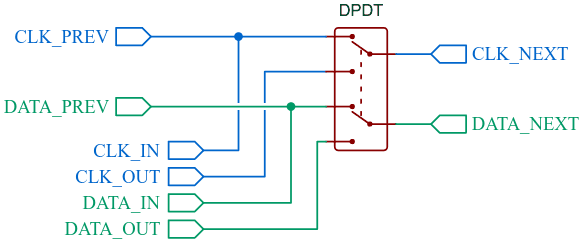

For example, if a module is connected to a socket, the MISO and MOSI signals will be routed to the respective IDC so they arrive at the module. The serial output of the module will go back to the IDC and further onto the bus board. If no module is connected to a socket, the socket is bypassed, and the MISO and MOSI signals are routed further down the bus board, to the next socket.

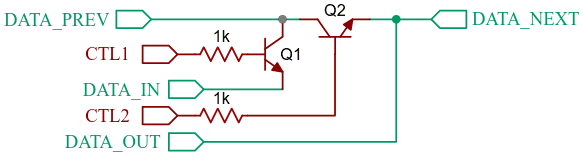

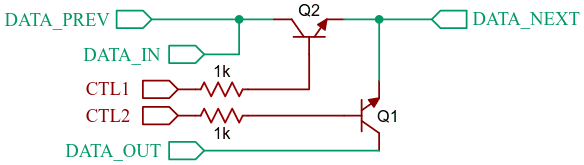

To do this, I'm using transistors that determine where the MISO and MOSI signals should go, for every socket. In the first 12 positions or so, this seems to be working fine, but close to the last positions, there is a lot of noise coming in. The traces on the bus board are 0.25mm wide, and the sockets are placed at 25mm from one another.

Could it be that the latch and clock signals are causing this, due to long distances? Is it OK to pass MISO and MOSI signals through several transistors?

I don't care to have a high speed with SPI, so I've tried slowing it down, but it doesn't help. Any tips on why this is not working and how I should solve this problem?

My goal is to build a plug-and-play bus board with generic code that should be loaded once to the Teensy.

Cheers

For example, if a module is connected to a socket, the MISO and MOSI signals will be routed to the respective IDC so they arrive at the module. The serial output of the module will go back to the IDC and further onto the bus board. If no module is connected to a socket, the socket is bypassed, and the MISO and MOSI signals are routed further down the bus board, to the next socket.

To do this, I'm using transistors that determine where the MISO and MOSI signals should go, for every socket. In the first 12 positions or so, this seems to be working fine, but close to the last positions, there is a lot of noise coming in. The traces on the bus board are 0.25mm wide, and the sockets are placed at 25mm from one another.

Could it be that the latch and clock signals are causing this, due to long distances? Is it OK to pass MISO and MOSI signals through several transistors?

I don't care to have a high speed with SPI, so I've tried slowing it down, but it doesn't help. Any tips on why this is not working and how I should solve this problem?

My goal is to build a plug-and-play bus board with generic code that should be loaded once to the Teensy.

Cheers