I am working on a project that requires sampling 32bit data at 30kHz on 64 channels. Currently, I am only able to push the sampling rate to be at 7.4kHz. Teensy4.1 is overclocked to 960 MHz and the SPI ckockin is 21M. Is there a way to feasibly achieve the desired sampling rate? Open to adding on a separate SPI driver if necessary but would appreciate suggestions.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

SPI frequency too low for real-time data acquisition

- Thread starter bigdlin

- Start date

joepasquariello

Well-known member

You don't say what how many SPI devices or what type, but assuming there are at least 3, Teensy 4.0 has 3 x SPI, so you could at least triple your throughput by using them all.

PaulStoffregen

Well-known member

Maybe the SPI async functions can help use 2 or 3 SPI ports more effectively?

Most ADC chips have some overhead, like a command byte before the data transfer. Even with no overhead, 32 bits times 64 channels times 30 kHz sample rate is 61.44 Mbit/sec. You'll probably need to use all 3 ports in parallel.

What you'll actually do with so much data at that speed is also a good (difficult) question.

Most ADC chips have some overhead, like a command byte before the data transfer. Even with no overhead, 32 bits times 64 channels times 30 kHz sample rate is 61.44 Mbit/sec. You'll probably need to use all 3 ports in parallel.

What you'll actually do with so much data at that speed is also a good (difficult) question.

mborgerson

Well-known member

This sounds like the kind of problem I'm thinking about in my NYWWIP (Not-Yet-Working_Work-In-Progress). If I get it working, one T4.1 would handle two SPI converters and send the data to T4.1 #2 over a fast, block-oriented USB link with minimal foreground CPU overhead. T4.1 # 2 would handle two SPI converters and merge the data from the two systems into blocks written to SD card. The overall data rate, at about 8MB/second is well within the capabilities of the SD card write rates (with appropriate buffering). At that point, you add MTP to get the data to the PC and let MATLAB or Python sort out the results. Simulating this collection sounds like a good example program for when I get USB_block_xfer working.Maybe the SPI async functions can help use 2 or 3 SPI ports more effectively?

Most ADC chips have some overhead, like a command byte before the data transfer. Even with no overhead, 32 bits times 64 channels times 30 kHz sample rate is 61.44 Mbit/sec. You'll probably need to use all 3 ports in parallel.

What you'll actually do with so much data at that speed is also a good (difficult) question.

You’ll probably need to go DMA SPI. With lots of interrupts handling. And a timer to get the 30 kHz sample trigger pulse. Can be done, i did something similar some time ago, and shared code for a T4_DMA_SPI class. A train of SPI ‘transactions’ needs to be defined in a table upfront.

What’s the data / SPI slave chip? Is it ADCs? MEMS? A camera?

Is it 3 or 4 wire SPI? Daisy chained or paralel?

link with code

What’s the data / SPI slave chip? Is it ADCs? MEMS? A camera?

Is it 3 or 4 wire SPI? Daisy chained or paralel?

link with code

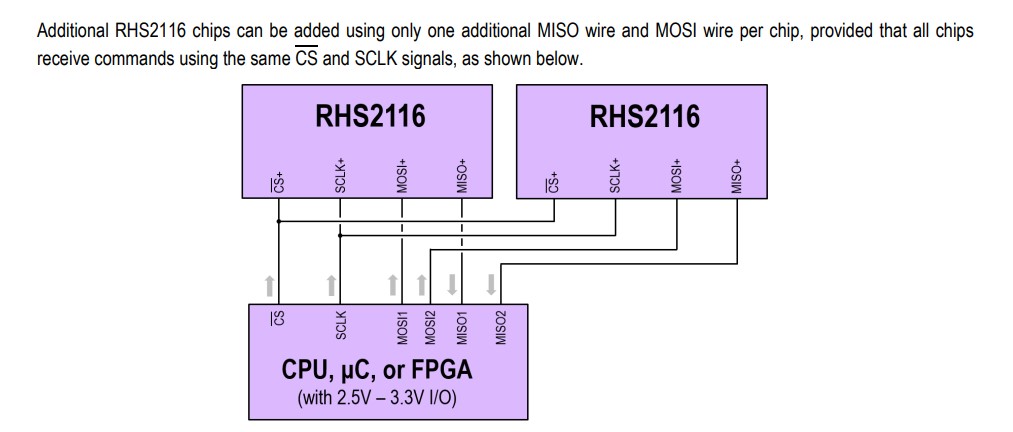

I am using 4 intan rhs chips. It's ADC in parallel.

This seems very curious and not the norm:

Typically the SPI bus is shared and additional CS lines are used to select the chip you want to talk to. Why are they doing it this way?

bigDlin do you have them wired this way? Is it working?

Also I meant to ask previously, have you tried running the SPI clock faster?

Typically the SPI bus is shared and additional CS lines are used to select the chip you want to talk to. Why are they doing it this way?

bigDlin do you have them wired this way? Is it working?

Also I meant to ask previously, have you tried running the SPI clock faster?

@strud, Intan Tech uses opalkelly as the controller, so it can do 4 SPI ports. On my teensy I'm using 2 SPIs and 4 CSs. I did try to increase the SPI frequency. it'll read back junk when I increase it from 21-22MHz. Thats why I set 21MHz as the max speed. Might be a technical limitation of my design. Regardless, is there a recommendation on an external SPI controller to use to make my life easier?