Hi everyone,

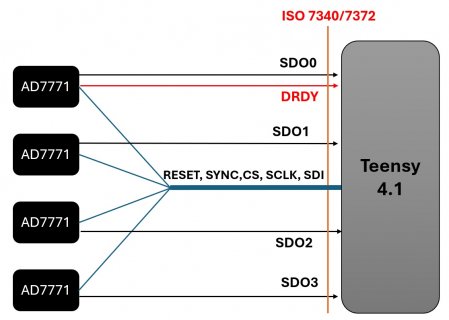

for a university project I am trying to implement simultaneous readout from multiple AD7771 at high speed without using an FPGA (learning curve and time commitment too high). The idea is to use the Teensy 4.1 to implement SPI by bit banging, request data from the ADCs by shared SPI inputs (to the ADC) and read simultaneously by separate output lines. All ADCs are synchronized by using the same local clock source and RESET/SYNC pins so all the data becomes available at the same time. SPI signals are passed between ADCs and MCU through isolators (ISO7340/7342) due to project requirements.

I had a PCB made and wrote some simple Teensy code, where I wait for an interrupt from the DRDY pin on the first ADC, then read data from all channels through SPI and stream it to PC through serial/USB.

I achieved correct readout on the first ADC at relatively slow SPI by placing small delays (delayNanoseconds) in the code after every digital read/write, but need to go much faster to push through all the data before consecutive ADC readings. Supported speed is 30MHz for AD7771 and 25Mbps for the ISO7340/7342. To clarify, Teensy would be fast enough for my purpose (all SPI comm within 20us) with no delays but in this conditions readout is broken. Problem is, when I reduce or remove the delays in the code, readings become rubbish or flat out zero. I checked the digital signals post-isolator (ADC side) and found the shape of the SCLK signal seriously degrades with increasing speed (see image). Other SPI pins are fine. The SCLK signal tends to shrink in amplitude and get closer to the VDD/2 value (VDD=3.3V).

I understand this is not an issue directly related to the Teensy, especially since the isolator is involved, but I was wondering if I am missing something or there is something I can do on the MCU side to improve clock shape while maintaining high-speed and no delays in code? Please see attached images for further explanation.

Any advice is appreciated. Many thanks.

for a university project I am trying to implement simultaneous readout from multiple AD7771 at high speed without using an FPGA (learning curve and time commitment too high). The idea is to use the Teensy 4.1 to implement SPI by bit banging, request data from the ADCs by shared SPI inputs (to the ADC) and read simultaneously by separate output lines. All ADCs are synchronized by using the same local clock source and RESET/SYNC pins so all the data becomes available at the same time. SPI signals are passed between ADCs and MCU through isolators (ISO7340/7342) due to project requirements.

I had a PCB made and wrote some simple Teensy code, where I wait for an interrupt from the DRDY pin on the first ADC, then read data from all channels through SPI and stream it to PC through serial/USB.

I achieved correct readout on the first ADC at relatively slow SPI by placing small delays (delayNanoseconds) in the code after every digital read/write, but need to go much faster to push through all the data before consecutive ADC readings. Supported speed is 30MHz for AD7771 and 25Mbps for the ISO7340/7342. To clarify, Teensy would be fast enough for my purpose (all SPI comm within 20us) with no delays but in this conditions readout is broken. Problem is, when I reduce or remove the delays in the code, readings become rubbish or flat out zero. I checked the digital signals post-isolator (ADC side) and found the shape of the SCLK signal seriously degrades with increasing speed (see image). Other SPI pins are fine. The SCLK signal tends to shrink in amplitude and get closer to the VDD/2 value (VDD=3.3V).

I understand this is not an issue directly related to the Teensy, especially since the isolator is involved, but I was wondering if I am missing something or there is something I can do on the MCU side to improve clock shape while maintaining high-speed and no delays in code? Please see attached images for further explanation.

Any advice is appreciated. Many thanks.