I'd like to know the maximum SPI clock that a Teensy4 can support. Wading through some of the NXP documents (which is painful), the normal LPSPI clock is limited to f_peripheralclock/2. Can't seem to find where or how to set this peripheral clock and what it's limits are. Can someone let me know what f_max would be for the SPI clock? And as a bonus, how one would set it to that speed?

My application is an external ADC, but I haven't chosen it yet. Would really like to know how fast one can practically read a 16 bit ADC using SPI. It affects my choice of ADC.

From what I understand there is a FlexSPI, which is supposedly faster, but honestly don't know how to use it. It seems in FlexIOSPI_simple.ino the example is limited to a 20Mbps clock. That doesn't seem faster than LPSPI. Or is that example limited by the writer's oscilloscope?

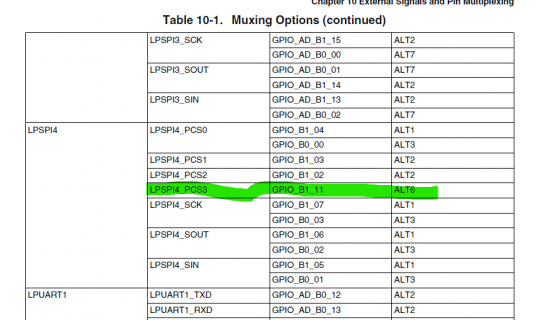

Is it possible to use QSPI? If I give up using the SD card (and other external memory) on a 4.1, is it possible to interface to an ADC that way? That would reduce the clock speed by a factor of 4.

Any insights on this would be helpful.

Looking to add a better ADC to digitize PIN diode detector pulses for metal identification. A lot of SW has been written, but the onboard ADC is not up to the task. Not enough ENOB.

My application is an external ADC, but I haven't chosen it yet. Would really like to know how fast one can practically read a 16 bit ADC using SPI. It affects my choice of ADC.

From what I understand there is a FlexSPI, which is supposedly faster, but honestly don't know how to use it. It seems in FlexIOSPI_simple.ino the example is limited to a 20Mbps clock. That doesn't seem faster than LPSPI. Or is that example limited by the writer's oscilloscope?

Is it possible to use QSPI? If I give up using the SD card (and other external memory) on a 4.1, is it possible to interface to an ADC that way? That would reduce the clock speed by a factor of 4.

Any insights on this would be helpful.

Looking to add a better ADC to digitize PIN diode detector pulses for metal identification. A lot of SW has been written, but the onboard ADC is not up to the task. Not enough ENOB.