For some time now I've been trying to find a way to have a continuously variable output sampling rate solution for T4.x to take the place of the ever more precarious T3.6 situation.

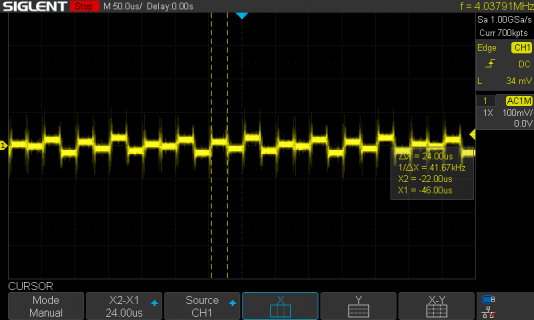

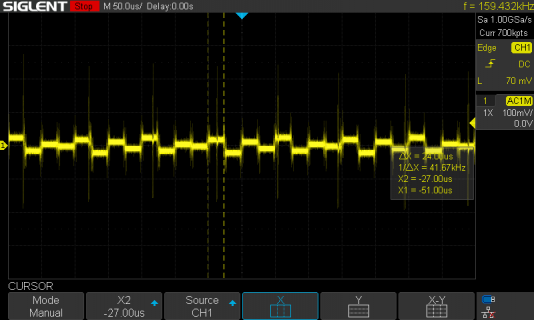

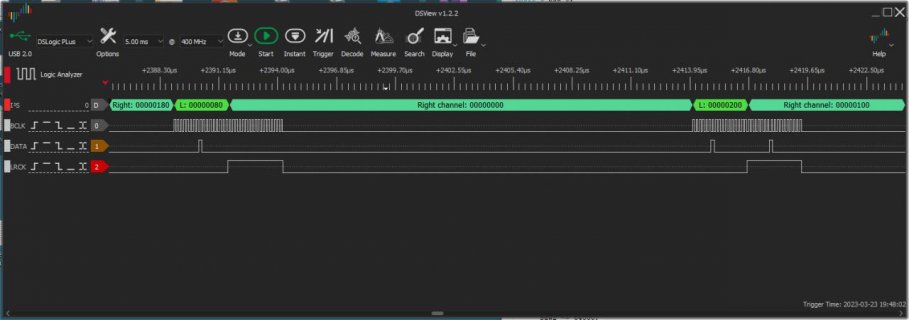

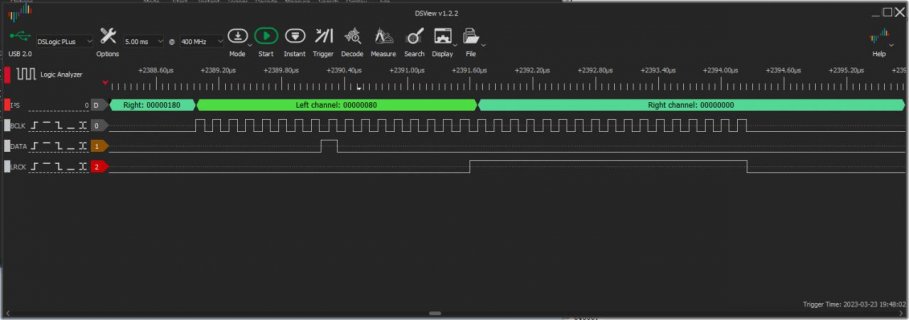

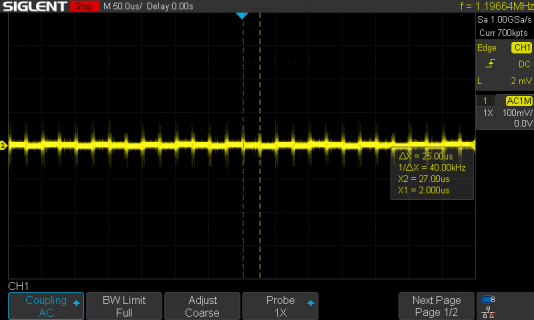

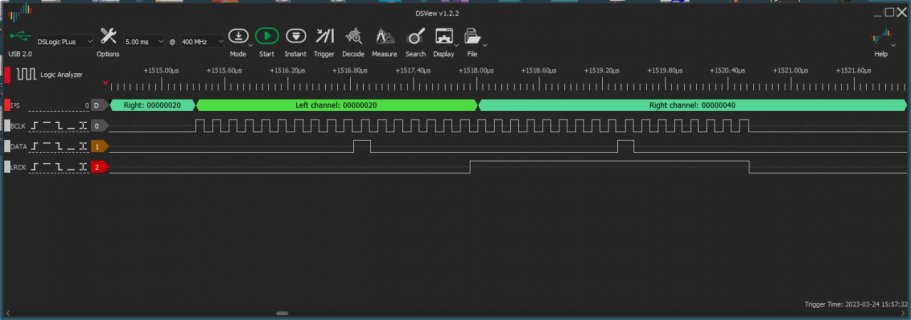

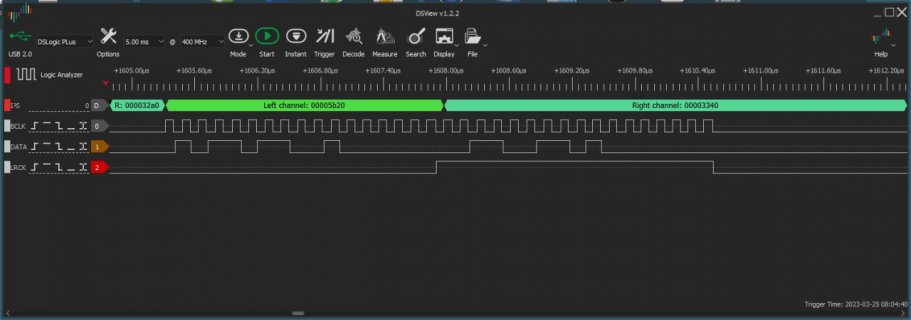

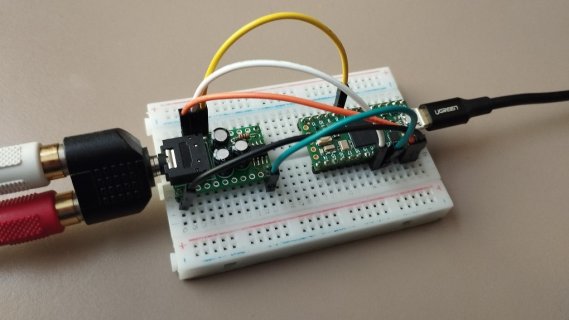

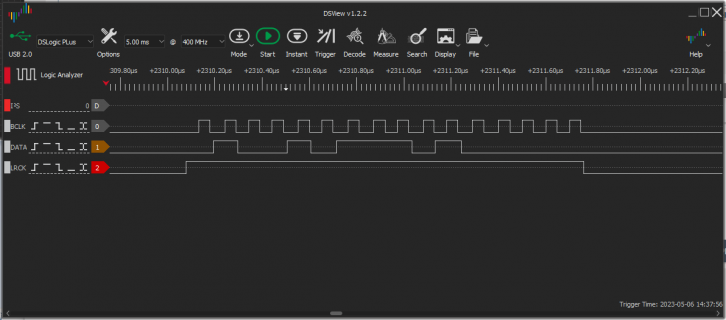

While adding a parallel DAC is going to be my last resort, I was wondering if a serial DAC like the PT8211 can be used by 'manually clocking' data from the T4. i.e. rather than set up the I2S interface, use a dedicated bit-toggling routine to send the correct states to three digital output pins (these could still be pins 7,20,21).

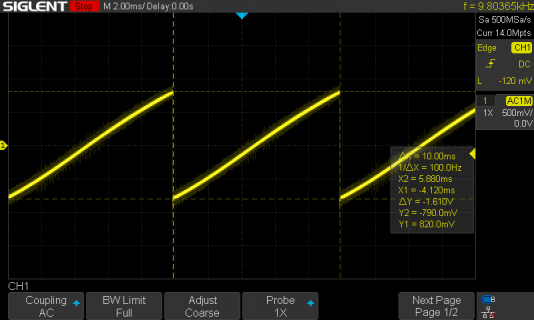

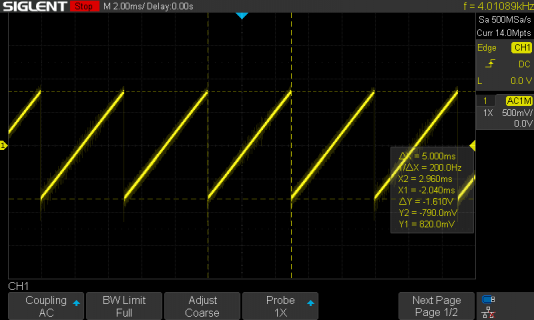

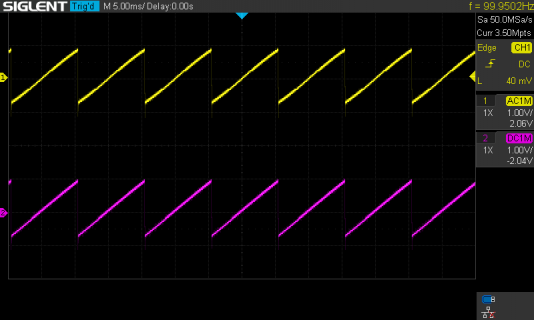

The idea would be to call that routine at the time I would normally write to the DAC on a T3.6, and have it send the three "serial signals" at something close to the max rate the PT8211 can handle, and then have them sit idle until the next DAC output is needed.

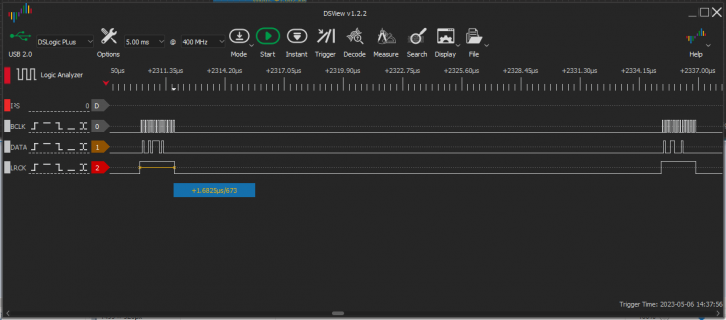

Is this at all plausible with something like the PT8211 (or alternative suggestions), or will serial DACs like this fall over in a heap because they need a steady clock/data/WS stream?

I looked at the PT8211 data sheet, but it's very concise and the timing diagram is not very helpful. The sheet says the chip allows a wide range of frequencies, and throws away data beyond 16 bits, but I can't see how it determines when the MSB is available.

While adding a parallel DAC is going to be my last resort, I was wondering if a serial DAC like the PT8211 can be used by 'manually clocking' data from the T4. i.e. rather than set up the I2S interface, use a dedicated bit-toggling routine to send the correct states to three digital output pins (these could still be pins 7,20,21).

The idea would be to call that routine at the time I would normally write to the DAC on a T3.6, and have it send the three "serial signals" at something close to the max rate the PT8211 can handle, and then have them sit idle until the next DAC output is needed.

Is this at all plausible with something like the PT8211 (or alternative suggestions), or will serial DACs like this fall over in a heap because they need a steady clock/data/WS stream?

I looked at the PT8211 data sheet, but it's very concise and the timing diagram is not very helpful. The sheet says the chip allows a wide range of frequencies, and throws away data beyond 16 bits, but I can't see how it determines when the MSB is available.