defragster

Senior Member+

Works 'well enough' ... For TYQT to get the serial # it has to pass through bootloader mode - which is what is need to program. TYQT does talk serial - and it should be there but without a change in startup I was wondering how that could be.

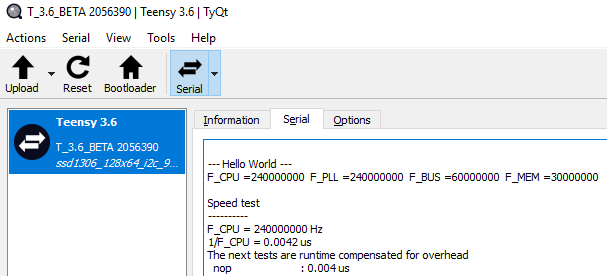

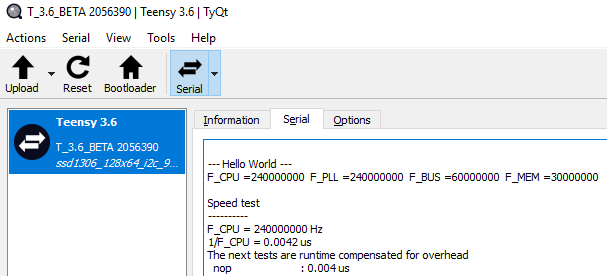

This at 240 MHz on a T_3.6 with fresh IDE 1.6.12 and TD_1.31b1 with no hacks. I saw it working well enough after the bootloader update.

Given my time with EEPROM and HSRUN OFF/ON I just did this and it works - HighSpeed T_3.6 serial number known at USB connect- interrupts are already disabled so it should be safe:

<EDIT> : Pull request below

@KurtE - please test this - it has worked for HOURS doing EEPROM I/O much more extensive - I think this is a good answer.

Note: My latest testing did plenty of USB SPEW before and after repeated continuous EEPROM writes over days and USB was never broken.

Paul - hopefully you get to go non-stop - running through spare airports is no fun.

Indeed @MM - there are lots of ways to get proto boards - but that one was new to me and seemed a perfect fit to usable mount devices and headers. With the pre-connected bottom sets most through hole connects on the bottom would be clean with less manual soldering, though both sides plated is more flexible. I made an AdaFruit Perma Proto 1/2 sized as the adapter for the top socketed PROTO and Beta units and it was very handy with pins soldered down and sockets soldered up.

This at 240 MHz on a T_3.6 with fresh IDE 1.6.12 and TD_1.31b1 with no hacks. I saw it working well enough after the bootloader update.

Given my time with EEPROM and HSRUN OFF/ON I just did this and it works - HighSpeed T_3.6 serial number known at USB connect- interrupts are already disabled so it should be safe:

<EDIT> : Pull request below

@KurtE - please test this - it has worked for HOURS doing EEPROM I/O much more extensive - I think this is a good answer.

Note: My latest testing did plenty of USB SPEW before and after repeated continuous EEPROM writes over days and USB was never broken.

Paul - hopefully you get to go non-stop - running through spare airports is no fun.

Indeed @MM - there are lots of ways to get proto boards - but that one was new to me and seemed a perfect fit to usable mount devices and headers. With the pre-connected bottom sets most through hole connects on the bottom would be clean with less manual soldering, though both sides plated is more flexible. I made an AdaFruit Perma Proto 1/2 sized as the adapter for the top socketed PROTO and Beta units and it was very handy with pins soldered down and sockets soldered up.

Last edited: